MOTOROLA Semiconductor Products Inc.

**INTRODUCTION**

PHASE-DETECTORS

OSCILLATORS - MULTIVIBRATORS

MIXERS

COUNTERS

APPLICATIONS

PACKAGING

# PHASE-LOCKED LOOP DATA BOOK

Second Edition August, 1973

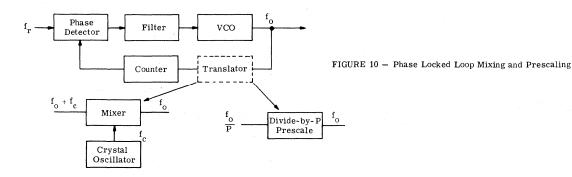

## MECL, MECL III, MECL 10,000, MTTL, and McMOS are trademarks of Motorola Inc.

Circuit diagrams external to Motorola products are included as a means of illustrating typical semiconductor applications; consequently, complete information sufficient for construction purposes is not necessarily given. The information in this book has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of Motorola Inc. or others.

©MOTOROLA INC., 1973 "All Rights Reserved"

#### **CONTENTS**

|                                                                                | Page No. |

|--------------------------------------------------------------------------------|----------|

| PURPOSE AND INTRODUCTION                                                       | . 1      |

| PHASE-LOCKED LOOP COMPONENTS                                                   | . 4      |

| PHASE-DETECTORS                                                                | . 18     |

| Phase-Frequency Detector; MC4344, MC4044,                                      | . 19     |

| Phase-Frequency Detector, MC12040                                              | . 38     |

| OSCILLATORS - MULTIVIBRATORS                                                   | . 42     |

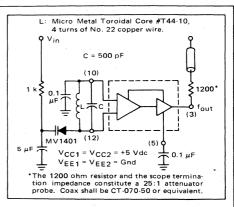

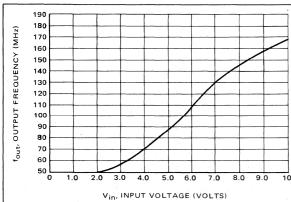

| Voltage-Controlled Oscillator; MC1648                                          | . 43     |

| Dual Voltage-Controlled Multivibrator; MC4324, MC4024                          | . 50     |

| MIXERS                                                                         | . 57     |

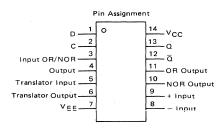

| Digital Mixer/Translator; MC12000                                              | . 58     |

| COUNTERS                                                                       | . 69     |

| Counter Selector Guide                                                         | . 70     |

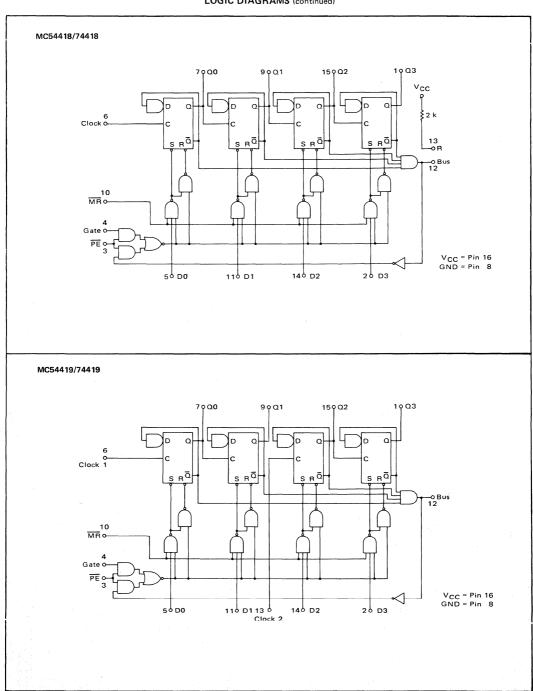

| Programmable Modulo-N Counters; MC54/74416, MC54/74417, MC54/74418, MC54/74419 | . 79     |

| Two-Modulus Prescaler; MC12012                                                 | . 94     |

| Counter Control Logic; MC12014                                                 | . 109    |

| APPLICATION NOTES                                                              | . 122    |

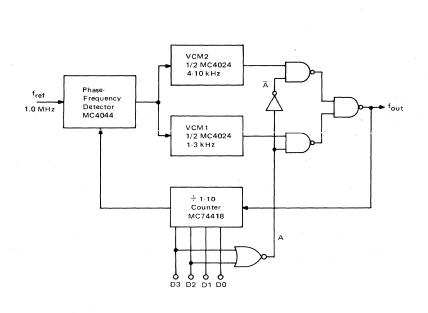

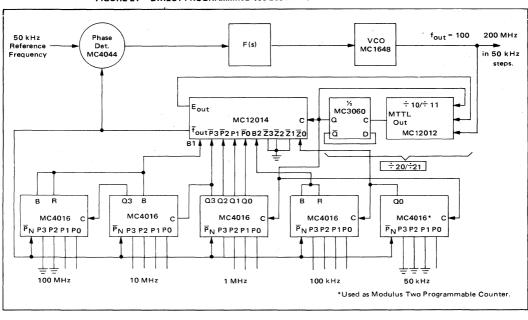

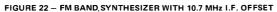

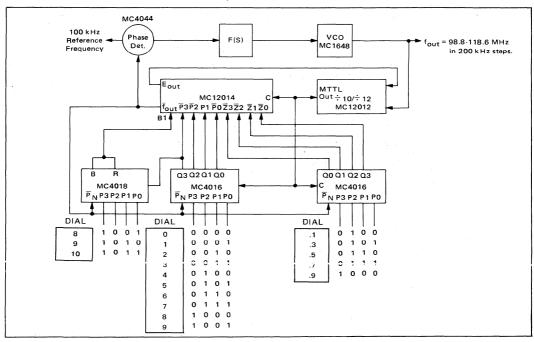

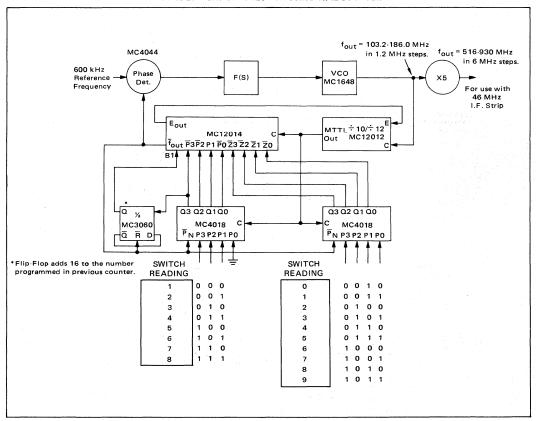

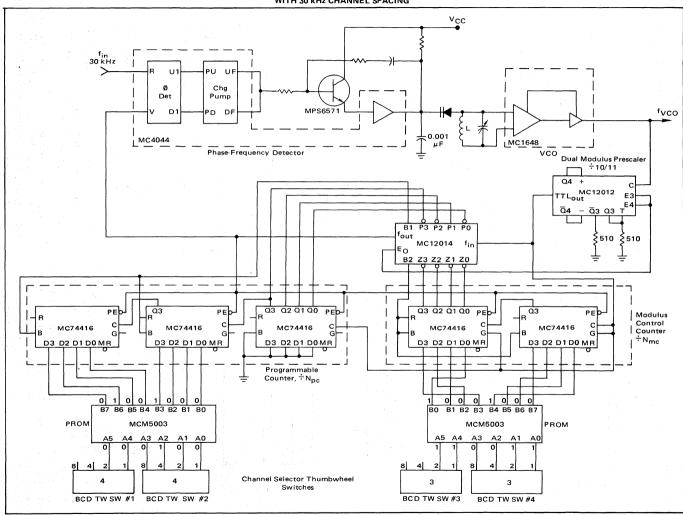

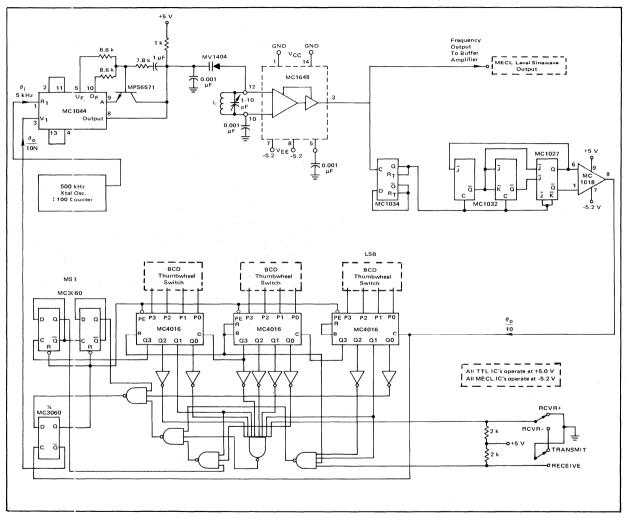

| MTTL and MECL Avionics Digital Frequency Synthesizer                           | . 123    |

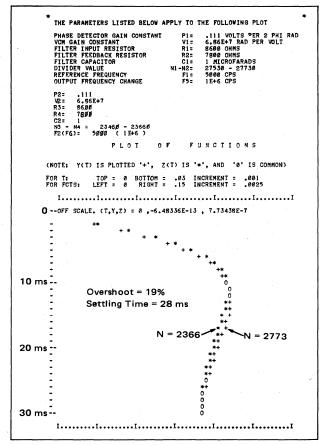

| Phase-Locked Loop Design Fundamentals                                          | . 133    |

| Medium Scale Integration in the Numerical Control Field                        | . 143    |

| A New Generation of Integrated Avionics Synthesizers                           | . 153    |

| An ADF Frequency Synthesizer Utilizing Phase-Locked Loop IC's                  | . 162    |

| PACKAGING INFORMATION                                                          | . 170    |

| APPLICATIONS ASSISTANCE                                                        |          |

| KEEPING UP TO DATE                                                             |          |

### **PURPOSE**

What is presented here is a complete set of hardware that is used for the assembly of phase-locked loop frequency synthesizers. Each of the functions is compatible with its own logic family, as well as being capable of interfacing with other logic families through suitable translating circuits.

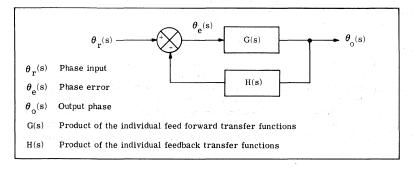

The circuits are optimized as independent entities rather than for a specific system, thereby increasing the system designer's flexibility. Equations for loop stability and bandwidth are discussed in the MC4344/4044 data sheet, and in application notes AN-532A and AN-535.

The new concepts presented are "digital harmonic mixing" and "digital phase detection". Harmonic mixing allows the generation of very high frequencies from one stable low frequency source. The system then need contain only one "tuned circuit" which is electronically variable and self aligning. Mixing itself requires no critical tank circuits and makes use of the narrow bandpass characteristics of the loop. Mixing can be combined with programmable counters or continuously-tuned oscillators to produce variable frequencies.

The digital phase detector's significance is its ability to discriminate both phase and frequency. The loop locks only on the fundamental and has a capture range limited only by the VCO range.

#### INTRODUCTION

Electronic phase locked loops (PLL) came into vogue in the 1930's when they were used for radar synchronization and communication applications. This technique for electronic frequency control is used today in satellite communication systems, airborne navigation systems, FM communication systems, computers, etc.

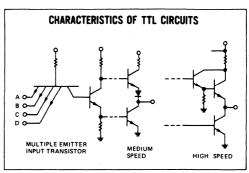

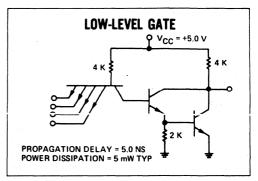

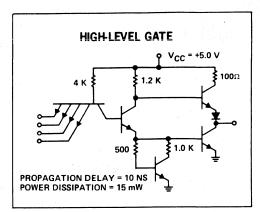

Motorola offers the designer a choice of specially designed integrated circuits for performing phase-locked loop functions: phase detection, frequency division, filtering, and voltage-controlled signal generation. This selection of functions permits the construction of reliable, high-performance loops of small size and low cost. In addition, the choice of circuits permits the designer to select TTL circuits where speed is not critical (<30 MHz), or ECL circuits where high speed is required (up to 500 MHz).

The circuits discussed are suitable for frequency synthesis, synchronization of digital signals, and clock recovery from encoded digital data streams.

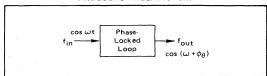

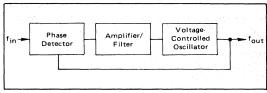

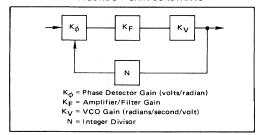

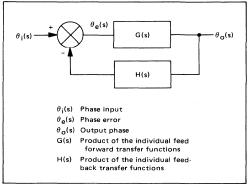

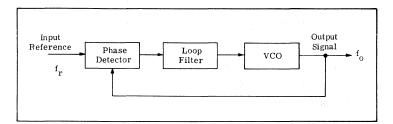

The basic PLL technique compares the frequency and phase of the incoming data to the output of a voltage controlled oscillator (VCO). If the two signals differ in frequency and/or phase, an error voltage is generated and applied to the VCO, causing it to

correct in the direction required for decreasing the difference. The correction procedure continues until lock is achieved, after which the VCO will continue to track the incoming signal.

These applications normally introduce two conflicting requirements: the system must very quickly lock-up to the incoming data and yet be capable of ignoring short term jitter inadvertantly introduced into the data. Using Motorola circuits, the required characteristics are established simply by selecting a few passive filter components. A typical application is discussed in more detail on the MC4344/4044 Phase-Frequency Detector data sheet.

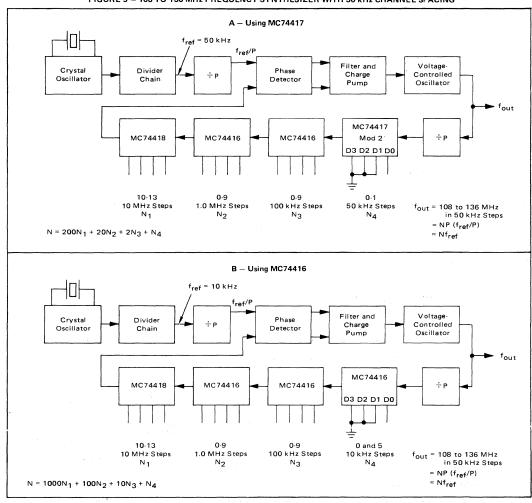

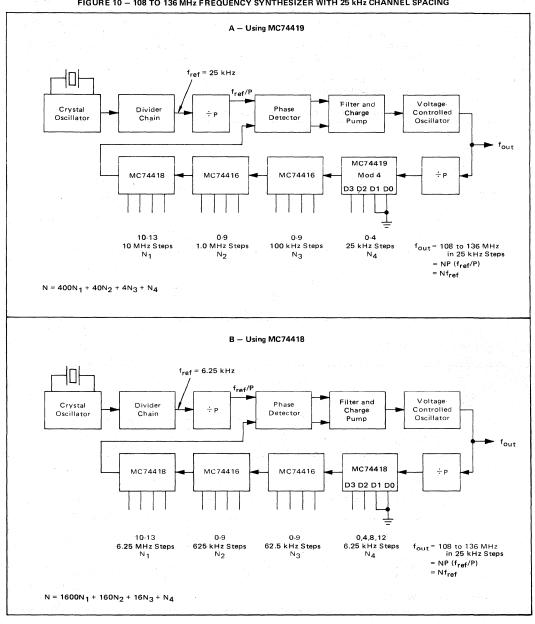

One of the major applications of the PLL is frequency synthesis in the many systems which require discrete frequencies or fixed-channel spacing. For examples, the UHF television band (channels 14-83) extends from 470 MHz to 890 MHz in 6 MHz steps, and the aircraft VHF navigation/communication band is 108 MHz to 136 MHz in 25 KHz steps. AM and FM standard broadcast bands are also in channel form.

Motorola's integrated circuits lend themselves extremely well to frequency synthesizers. The remainder of this section is devoted to a description of Motorola PLL integrated circuits and their application to frequency synthesizers. Other applications are discussed on the individual data sheets (e.g., MC12012 included in this brochure).

#### **Digital PLL Configurations**

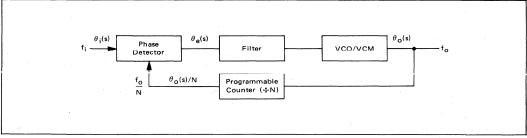

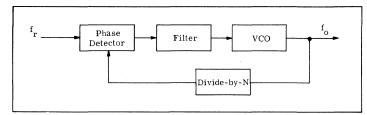

A number of frequency synthesizers that are tuneable in increments of a reference frequency,  $f_{\Gamma}$ , will be examined for economy and performance.

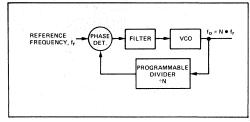

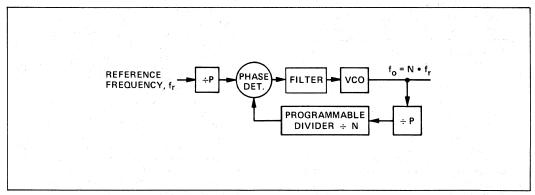

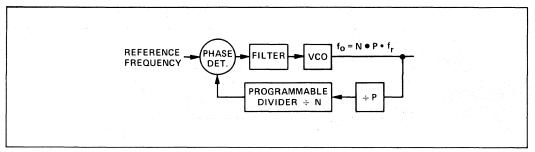

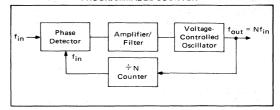

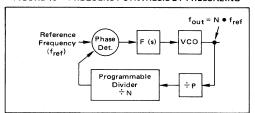

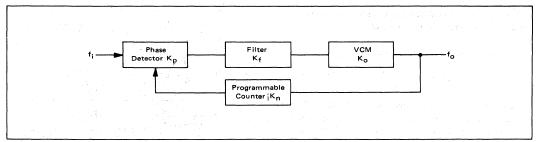

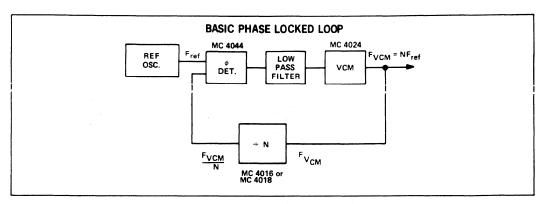

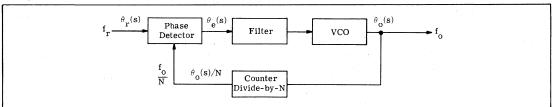

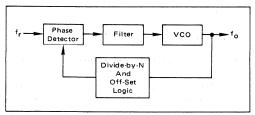

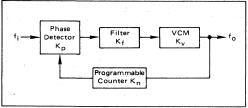

#### Direct PLL

Figure 1 is considered to be the direct approach. The output frequency is an integer multiple of the reference frequency ( $f_{out} = N f_r$ ). This is the simplest form that the loop can assume but not necessarily the least expensive at higher frequencies. The VCO must be capable of operating at the output frequency. This is easily accomplished, up to 200 MHz. However, the complex programmable counters would also be required to operate at these frequencies. To achieve such speeds, special techniques or devices are required. Because high frequency (>25 MHz) programmable counters are expensive, special techniques to program the output frequency will now be discussed.

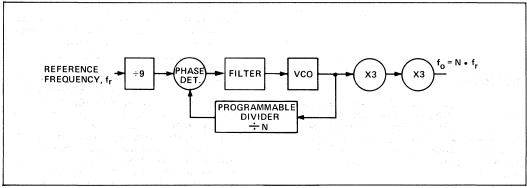

#### Multiplier PLL

In Figure 2, the input to the phase detector is  $f_r$  divided by 9, and the output of the VCO is multiplied by nine  $(f_O = N \cdot f_r)$ . Since a lower effective reference frequency is employed, the response of the loop to a change in N is necessarily slower.

In addition, the output frequency is an integer multiple of the VCO frequency and this generally requires the use of tuned tank circuits. No problem is encountered if a fixed frequency or very small change in frequency is required. However, the multiplier tank must have high enough  $\Omega$  to multiply correctly, but low enough  $\Omega$  for sufficient bandwidth over the desired tuning range. From a manufacturing standpoint there are economic disadvantages: the tank must be tuned. This necessarily raises costs, and also creates a need for periodic servicing.

A final disadvantage caused by multiplying the VCO is that any perturbations in the VCO frequency are correspondingly multiplied. Sidebands which are sub-audio (below 300 Hz) at the VCO frequency may lie in the audible range after multiplication.

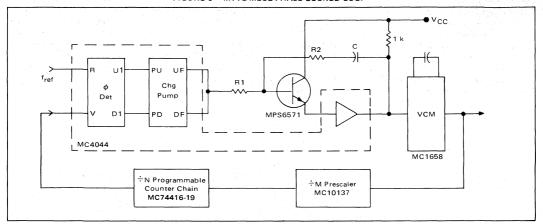

Figure 1 — Frequency Synthesis Using a Basic Phase-Locked Loop

Figure 2 — Frequency Synthesis Using a Phase-Locked Loop and Output Multipliers

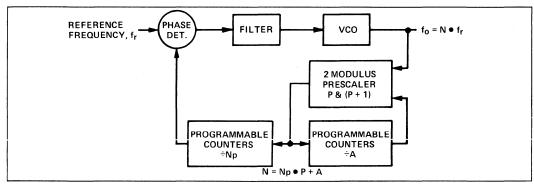

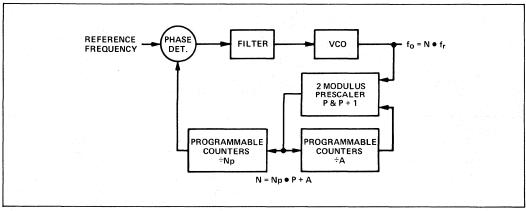

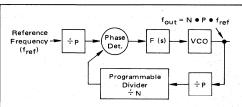

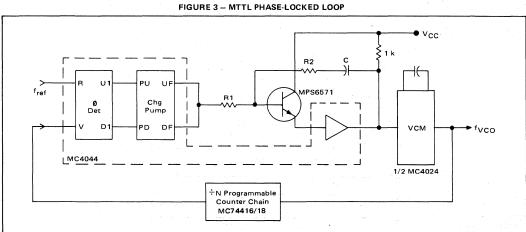

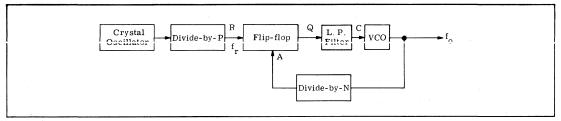

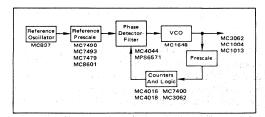

Figure 3 — Frequency Synthesis by Prescaling in the Phase-Locked Loop

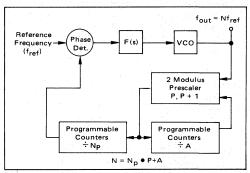

Figure 4 — Frequency Synthesis by Two Modulus Prescaling in the Phase-Locked Loop

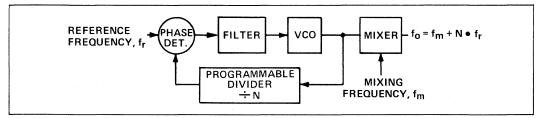

Figure 5 — Phase-Locked Loop Frequency Synthesis by Mixing Up

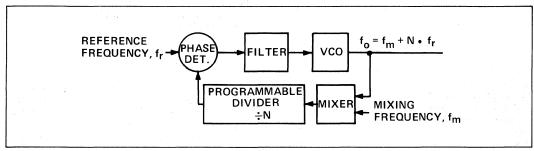

Figure 6 — Phase-Locked Loop Frequency Synthesis

#### Prescaler PLL

The system shown in Figure 3 is somewhat better than that in Figure 2 since it places the frequency multiplication inside the loop. The VCO is now required to deliver substantially higher frequencies, but the tuned multipliers are eliminated. The prescaler block ( $\dot{\tau}$  P) consists of a number of flip-flops connected as a fixed-divider chain. The input frequency into the divide by N is as low as that in Figure 2. Likewise, the loop response is slow.

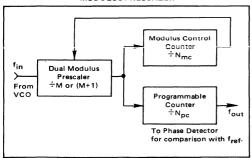

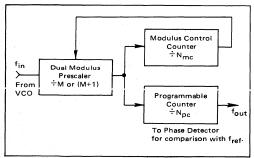

#### Two Modulus Prescaled PLL

The configuration shown in Figure 4 includes a prescaler with provision for varying the modulus (divisor). Control is by means of a low frequency programmable counter. While the cost of this system is slightly greater than that shown in Figure 3, the performance is equal to that of the system in Figure 1.

#### PLL with Mixing Up

Figure 5 is a departure from the previous two system configurations. The reference frequency is equal to the channel spacing, and  $f_0 = f_m + N \ f_r$ . This allows the VCO and logic a low operating frequency, but requires the generation of a fixed frequency ( $f_m$ ) to mix to the higher frequency. It also requires a tuned output in the mixer, thus restricting the allowable tuning range.

#### PLL with Mixing Down

In Figure 6 the VCO is required to operate at the high output frequency. A mixing frequency,  $f_m$ , must be generated as a heterodyning signal and the mixer must be capable of handling the required input frequencies.

In this configuration, the mixer is placed inside the loop so that the effect of the mixing oscillator on the output frequency is included in loop action. As in Figure 5,  $f_0 = f_m + N f_r$ .

## PHASE-LOCKED LOOP COMPONENTS

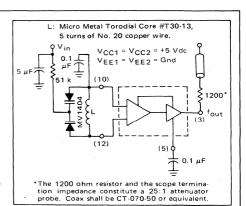

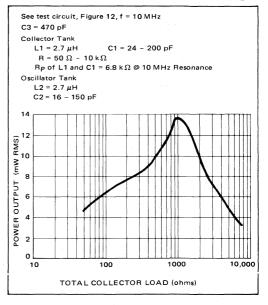

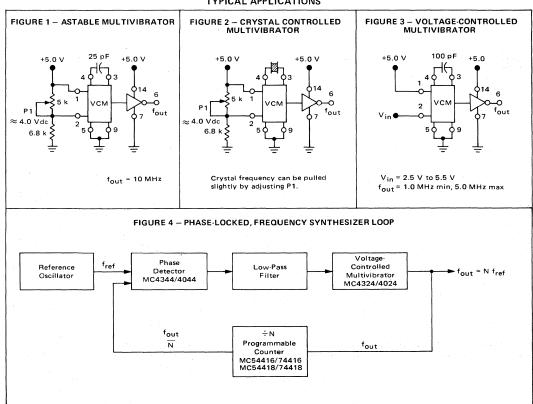

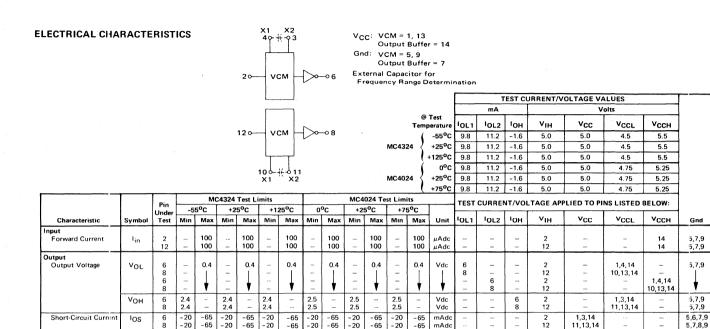

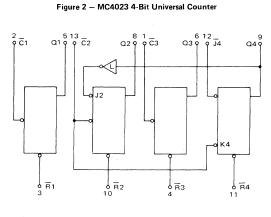

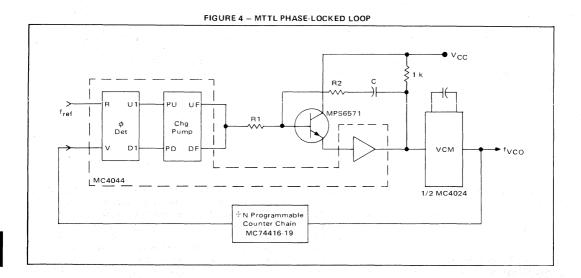

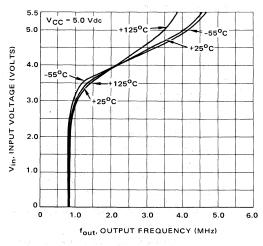

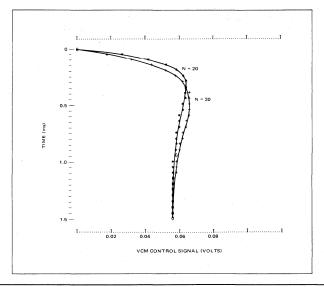

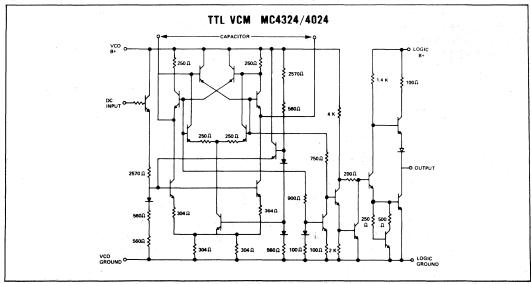

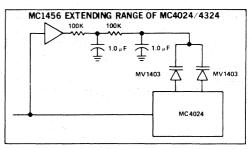

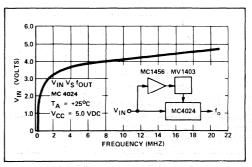

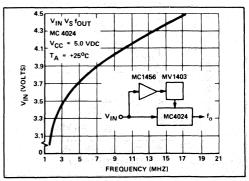

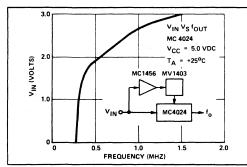

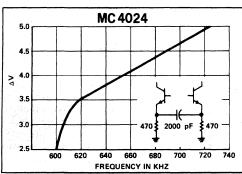

Voltage Controlled Multivibrators — VCM (MC4024, MC1658)

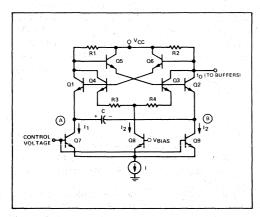

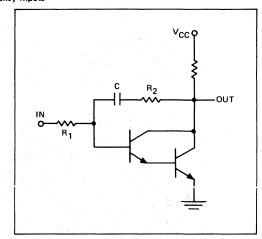

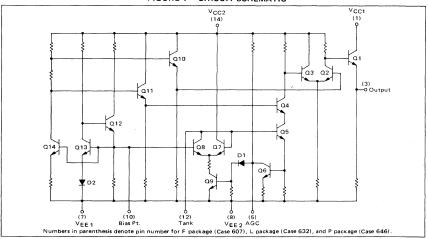

The MC4024 and MC1658 voltage controlled multivibrators have output levels compatible with the TTL and ECL Families respectively. Both multivibrators have a typical tuning range of 4:1. The multivibrator sections of both devices are similar; therefore, the operation of only one will be described. For purposes of explanation, Figure 7 shows a somewhat simplified version of the multivibrator section of the MC1658.

In Figure 7,  $Q_1$ ,  $Q_2$ ,  $Q_5$ ,  $R_1$  and  $R_2$  form a differential amplifier connected in a positive feedback configuration.  $Q_3$ ,  $Q_4$ ,  $Q_5$ ,  $Q_6$ ,  $R_1$ ,  $R_2$ ,  $R_3$  and  $R_4$  also form an amplifier connected for positive feedback. A common current source, I, is shared between the two amplifiers. The current I is divided between the amplifiers by means of  $Q_7$ ,  $Q_8$ , and  $Q_9$ .

The basic oscillator section consists of the first amplifier ( $Q_1$ ,  $Q_2$ , etc.) along with the timing capacitor, C, connected between the emitters of  $Q_1$  and  $Q_2$ . In this configuration the charging current for C is  $I_1$ , and is controlled by  $Q_7$  and  $Q_9$ .

The second amplifier (Q3, Q4, etc.) performs two major functions: 1) ensures proper and rapid switching of the multivibrator once the threshold voltage is reached; and 2) maintains a constant logic swing for the multivibrator over its entire tuning range. The latter helps maintain linear frequency-versus-voltage characteristics so desirable in voltage controlled multivibrators.

For a more detailed analysis of the operation of the multivibrator, consider the case when  $Q_2$  and  $Q_3$  have just turned on and  $Q_1$  and  $Q_4$  have turned off. The voltage across C at this time is  $V\ell$  with the polarity as indicated in Figure 7. Since  $Q_1$  and  $Q_4$  are off, no current flows through  $R_1$  and the voltage at the bases of  $Q_2$  and  $Q_3$  is (VCC  $^-$  VBE). Since  $Q_2$  and  $Q_3$  are on, the current through  $R_2$  is  $(2l_1+l_2)$

Figure 7 — Schematic of a Basic Voltage Controlled Multivibrator

and voltage of the bases of  $Q_1$  and  $Q_4$  is (VCC - VBE - R<sub>2</sub>I). With  $Q_2$  and  $Q_3$  conducting, the voltage at point B is (VCC - 2 VBE), while at point A is the voltage at point B plus the voltage across C, or (VCC - 2 VBE + V). For this condition the voltage across the emitter-base junction of  $Q_1$  is  $\begin{bmatrix} VCC - VBE - R_2I - (VCC - 2 VBE + V\ell) \end{bmatrix} = VBE - V\ell - R_2I$ ; the junction is reverse biased (assuming  $V\ell + R_2I > VBE$ ), and  $Q_1$  is off.

With  $Q_1$  and  $Q_4$  off it can be seen that  $I_2$  flows through  $Q_3$  and  $2I_1$  flows through  $Q_2$ . Since only  $I_1$  can flow through  $Q_9$ ,  $I_1$  must flow through C to  $Q_7$ . Capacitor C starts charging from ( $V_{CC}$  - 2  $V_{BE}$  +  $V_2$ ) toward  $V_{EE}$  at a rate equal to I/C. With point B held at a constant voltage of  $V_{CC}$  -  $V_{CC}$  -  $V_{CC}$  + the capacitor charges toward  $V_{CC}$  until point A reaches the threshold of  $V_{CC}$ , which is ( $V_{CC}$  -  $V_{CC}$  - V

Once the threshold voltage of  $\Omega_1$  is reached,  $\Omega_1$  starts to conduct. The current that flows through  $\Omega_1$  causes a corresponding voltage drop across  $R_1$ . This voltage drop lowers the voltage at the emitter of  $\Omega_2$ . This voltage is transferred via C to drive point A lower and causes  $\Omega_1$  to conduct more. In addition, as the current through  $\Omega_1$  increases, a corresponding decrease in current through  $\Omega_2$  occurs.

This decrease in current is reflected in a decrease of the voltage across  $R_2$  which raises the voltage at the base of  $Q_1$  causing further conduction.

At this point it becomes apparent that once the voltage at point A reaches the threshold of  $\Omega_1$ , the positive feedback of the circuit causes  $\Omega_1$  to turn on rapidly and switch  $I_1$  from C to  $R_1$ .

At some point during the switching of  $I_1$  to the collector of  $\Omega_1$ , the increase in the voltage across  $R_1$  and corresponding decrease in voltage across  $R_2$  cause the voltages at the bases of  $\Omega_3$  and  $\Omega_4$  to enter the transition region of the differential amplifier,  $\Omega_3$  and  $\Omega_4$ . Once the active region of the amplifier is reached,  $\Omega_4$  begins to conduct. Due to the positive feedback connection for these transistors the same regeneration action occurs as described for  $\Omega_1$  and  $\Omega_2$ , and  $\Omega_3$  is switched from  $\Omega_3$  to  $\Omega_4$ .

After switching,  $Q_1$  and  $Q_4$  are on.  $Q_2$  and  $Q_3$  are off, the voltage across the capacitor is  $V\ell=R_2I$  in a polarity opposite to the one indicated, and the voltage at point A is  $V_{CC}$  -  $2V_{BE}$ . The voltage at B is now  $V_{CC}$  -  $2V_{BE}$  +  $V\ell$ . One half cycle has been completed and the initial conditions stated are applied to the other half of the circuit. Ensuing operation is identical, and need not be discussed.

The differential amplifier ( $Q_3$  and  $Q_4$ ) plays an important role in the proper operation of the multivibrator. Resistors  $R_3$  and  $R_4$  must be made sufficiently large to ensure the multivibrator will enter the active region during the initial switching of either  $Q_1$  or  $Q_2$ . However, the resistors cannot be made so large that they decrease the gain of the amplifier to less than 1. If either of these conditions are not met, the multivibrator will not function properly.

For a given value of C, the frequency of the multivibrator is varied by changing the charging current 1<sub>1</sub> through the capacitor. 1<sub>1</sub> is varied by

means of the steering network:  $Q_7$ ,  $Q_8$ , and  $Q_9$ .  $Q_8$  is tied to a fixed bias voltage, while  $Q_7$  and  $Q_9$  are connected to the control voltage input. As the control voltage is increased,  $I_1$  through  $Q_7$  and  $Q_9$  increases and a corresponding decrease in  $I_2$  occurs. As  $I_1$  increases, C charges more rapidly and the frequency increases. From the previous discussion it may be noted that  $I_1$  could be decreased to point where the  $I_1$ - $R_1$  drop would be insufficient to reach the active region of  $Q_3$  and  $Q_4$ ; then the multivibrator would cease to operate. Both the MC4024 and MC1658 have internal, non-varying current sources shunting  $Q_7$  and  $Q_9$  to ensure this condition does not happen.

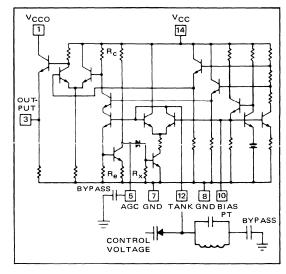

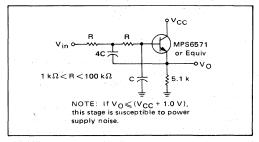

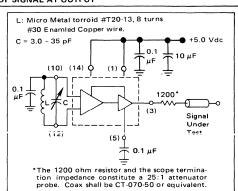

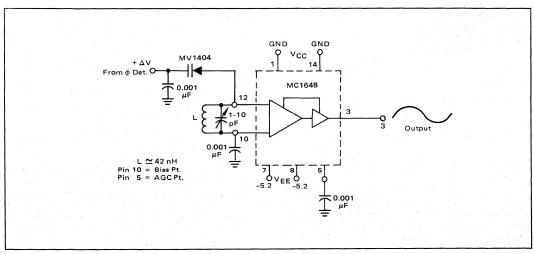

#### Oscillator (MC1648)

An LC oscillator, (Figure 8), is sometimes preferable to an RC multivibrator because of the inherently higher Q of the frequency determining circuits. This results in lower noise. Switching oscillators (multivibrators) generally have poorer spectral purity.

The MC1648 is composed of an emitter-coupled pair of transistors, biased through the tank circuit to cause regeneration. Since a large voltage swing would forward bias the base collector junction of one transistor of this pair, an automatic gain control is added by means of an emitter-follower from the tank circuit. AGC action limits the swing to Epp = 2  $\pi$  RE/RC (VCC  $^-$  2.2 VBE). A current source allows only enough current to flow so that this condition is met. In this circuit, component values were chosen to produce about a 500 mV peak-to-peak swing.

Since any additional load on the tank would decrease the Q of the oscillator and degrade spectral purity, a cascode transistor is used to couple from the emitter follower and to provide translation to a differential pair of transistors. These, in turn, produce a square wave compatible with existing ECL families. The output is highly buffered from the frequency determining components so that loading does not cause frequency shift.

Note that the tank circuit is approximately two diode drops above ground. This requires that the voltage on an external tuning mechanism be limited, or else capacitively isolated (see data sheet).

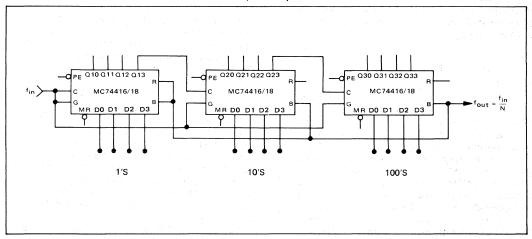

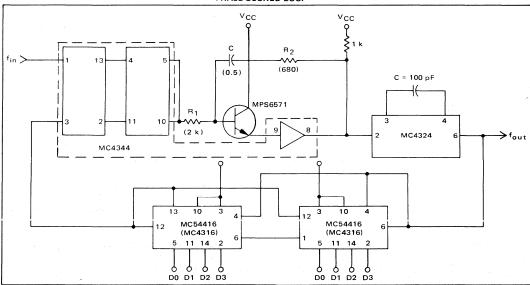

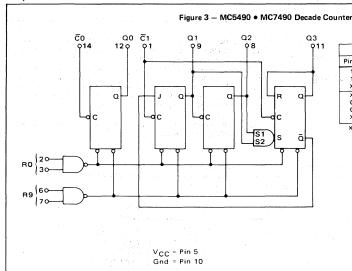

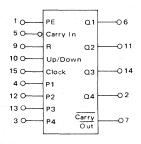

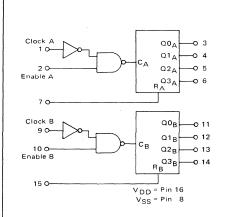

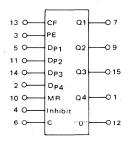

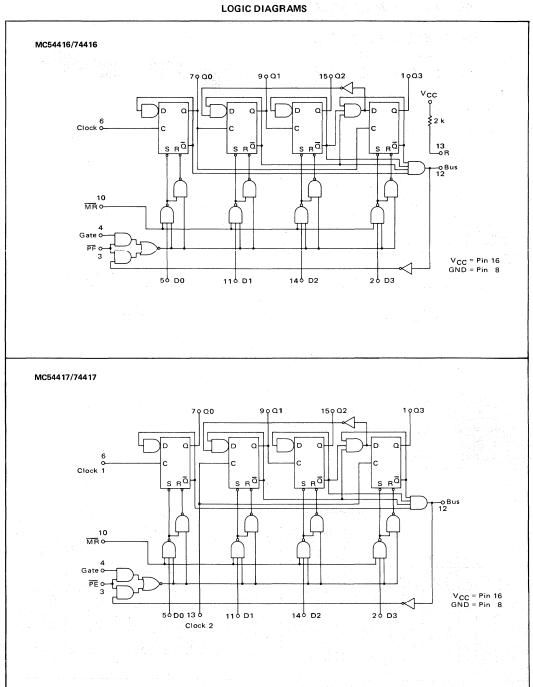

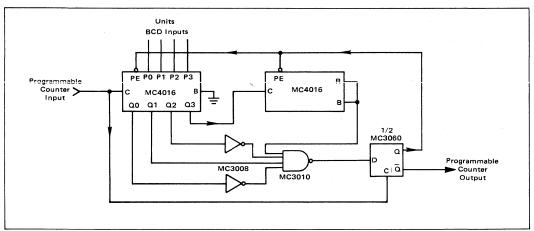

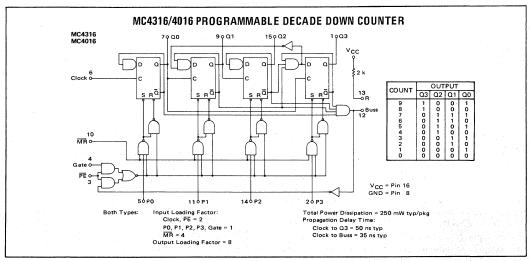

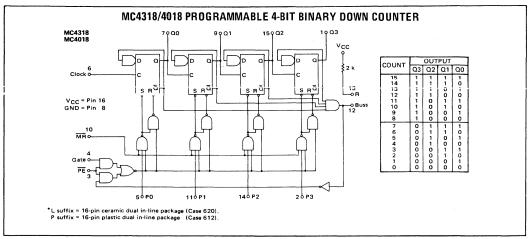

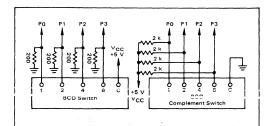

## Programmable Counting (MC74416 and MC74418)

Although there are many ways to design programmable counters, only programmable-down counting will be discussed here. The operation is quite simple: a number is preset into the counter, the clock is enabled and the counter cycles to zero, at which time the number is preset again. The operation is slightly more complicated when several packages are connected together to form a larger counter. The necessary connections must be available to insure that the system behaves as a unified entity.

For an example, consider a modulus 10 counter. The truth table for its operation is shown in Figure 9. From any given number, the counter must cycle to

Figure 8 - ECO with MECL Output

|                        | σ8 | 04 | 02 | 01 |

|------------------------|----|----|----|----|

|                        | D  | С  | В  | Α  |

|                        | 0  | 0  | 0  | 0  |

|                        | 1  | 0  | 0  | 1  |

| 01.001/11/0            | 1  | 0  | 0  | 0  |

| CLOCKING<br>TRANSITION | 0  | 1  | 1  | 1  |

| 0 – 1                  | 0  | 1  | 1  | 0  |

| <b>v</b> – 1           | 0  | 1  | 0  | 1  |

|                        | 0  | 1  | 0  | 0  |

|                        | 0  | 0  | 1  | 1  |

|                        | 0  | 0  | 1  | 0  |

|                        | 0  | 0  | 0  | 1  |

|                        | 0  | 0  | 0  | 0  |

Figure 9 - Counter State Table

0000, and then if no preset information is applied, must return to 1001 (9) and count down again. A ripple counter can be used in this application since the most significant bits return to the zero state first. Operating speed is limited by the toggle rate of the least significant bit (or first flip-flop in the chain), and the logic required to detect the zero and preset conditions.

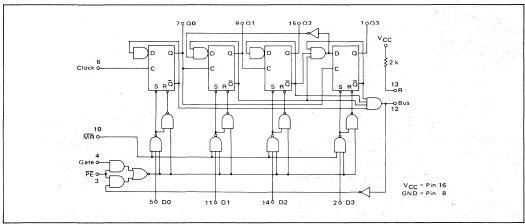

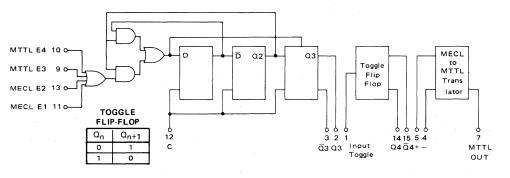

From an examination of Figure 9, it may be observed that the flip-flop to be used should change state on the positive going edge of the clock (transition from "0" to "1"). This may be accomplished with a D flip-flop if the  $\overline{\Omega}$  output is returned to the D input. The first three flip-flops are connected in the normal ripple fashion, but the last flip-flop's clock is driven from the  $\Omega$  output of the first flip-flop.

To detect the 0000 state, the Q outputs from the second and third flip-flops are ANDed at the input to

the fourth flip-flop, and the inverted result is ANDed with the toggle feedback to the second flip-flop. Logic connections are shown in Figure 10. The result of these interconnections is the transition from 0000 to 1001.

The basic counter must be capable of being preset to a given number when the counts of all decades reach zero. To detect the zero states requires the AND of all  $\overline{Q}s$  (or equivalent logic). For practical reasons it is not convenient to build a fan-in gate to do this. Thus each decade provides the NOR function of the Q outputs through an "open collector" gate.

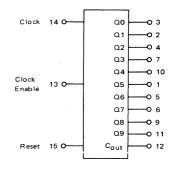

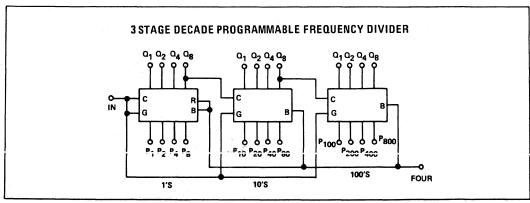

These outputs can be bussed or tied together with one common pull-up resistor as shown in Figure 11. All decades must have a 0 state (0000) if the output is to rise to a logic 1. It is this change in output level that effects preset of the programmed number.

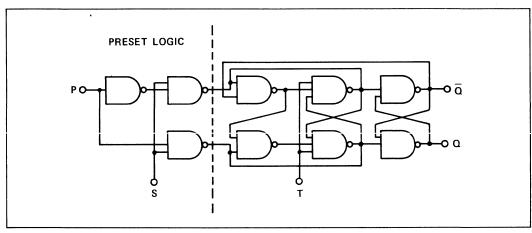

The preset function is accomplished on each flip-flop in the manner shown in Figure 12. This operation must override the effects of the clock input.

Consider presetting to 0001 from 0000. If the

preset did not suppress the clock the entire decade would ripple to 1111. This effect becomes more serious as the decades are cascaded. Also, it is desirable to have a predictable pulse width for the output frequency.

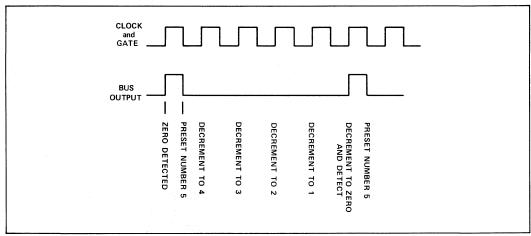

In the circuit of Figure 12, the output pulse width is equal to the pulse width of the input frequency. The reset pulse is inhibited until the 1 - 0 transition of the clock edge. This is accomplished by connecting the clock and gate inputs together as shown in the logic diagram of Figure 10. The clock and gate input, and bus output for a divide by 5 are shown in Figure 13.

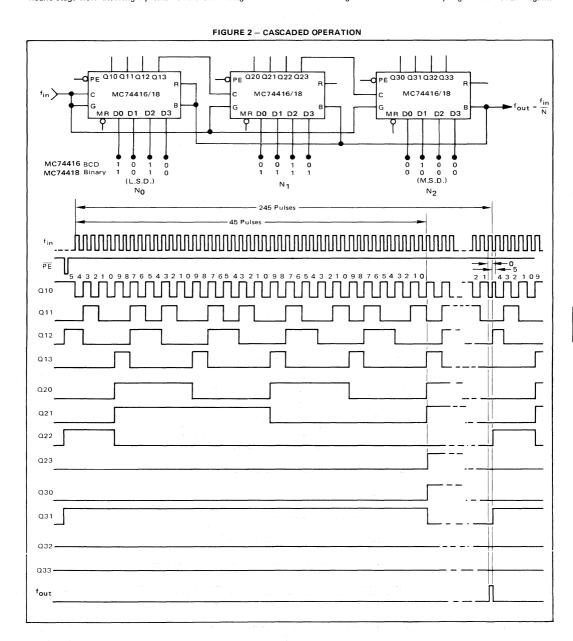

Figure 11 also illustrates how several decades may be cascaded. To examine the cascade's operation, consider division by 497 (0100 1001 0111). The least significant decade is decremented first. When the first decade count reaches 0000, the next pulse clocks it to a 9 (1001) and decrements the second decade by one count. The result is now 0100 1000 1001.

The second decade continues to be decremented once for every 10 pulses into the first decade. The third decade responds to the second decade in the

Figure 10 — Logic Diagram for an NBCD Programmable, Cascadeable, Divide By N Counter

Figure 11 - 3 Stage Programmable Decade Frequency Divider

Figure 12 - Presettable Counter Logic Element

Figure 13 — Presettable Counter Timing Diagram

Figure 14 - Frequency Extender

same manner that the second decade responds to the first.

It is important to note that the preset information tells the counter only where to start and is not the modulus of the counter.

In some applications a binary counter has been substituted for the decade counter for division through 1599 instead of 999. This is allowable since the most significant decade counts down only once and does not recycle. It is useful to notice that the most significant decade returns to zero before the other decades, permitting cascading with no loss in operating speed of the input frequency.

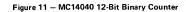

In Figure 11, the counter may be built with TTL logic. While the toggle rate of the flip-flops used would be in excess of 30 MHz, the speed of the presettable counter altogether will only be about 8 MHz. This does not meet the requirements set forth originally. Consequently a look-ahead technique has been developed so that the counter can be operated in excess of 25 MHz. The technique is called "frequency extension".

Figure 15 - Frequency Extender Timing Diagram

Figure 16 - Frequency Synthesis by Prescaling

Figure 17 - Frequency Synthesis by Two-Modulus Prescaling

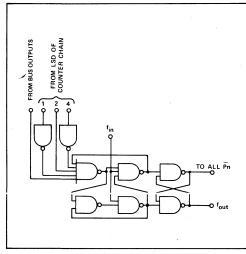

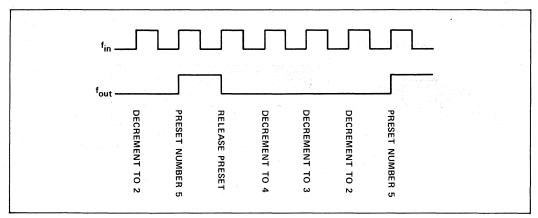

The frequency extender to be used consists of several gates connected to form a D flip-flop that detects the 0000... 0010 (2) state of the counter. The presets of the counter are activated on the first count and released on the zeroeth count. This logic is shown in Figure 14. The timing diagram and associated states are shown in Figure 15.

Notice that in Figure 13 the zero is detected after the clock makes a positive transition and the information is preset after the negative transition. This allows only half a cycle time for presetting as opposed to Figure 15 which allows a full cycle. Also, the

minimum clock width necessary to establish the pulse width from the bus gate is eliminated. The combination of the two factors allows about a three-fold increase in operating speed. The output frequency can be taken from the output synchronous with the input.

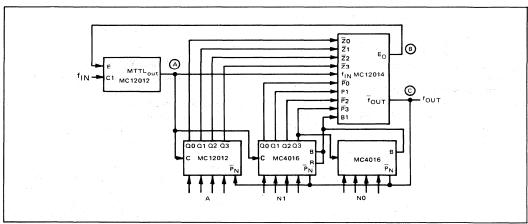

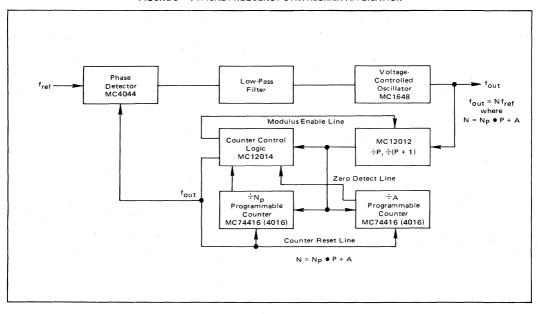

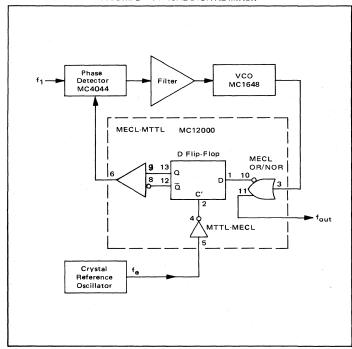

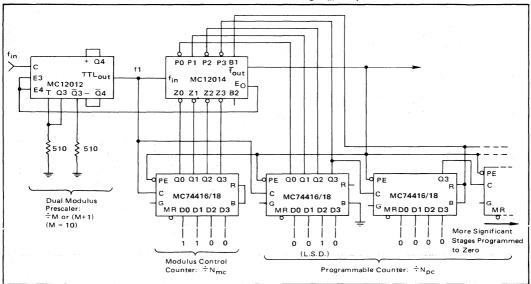

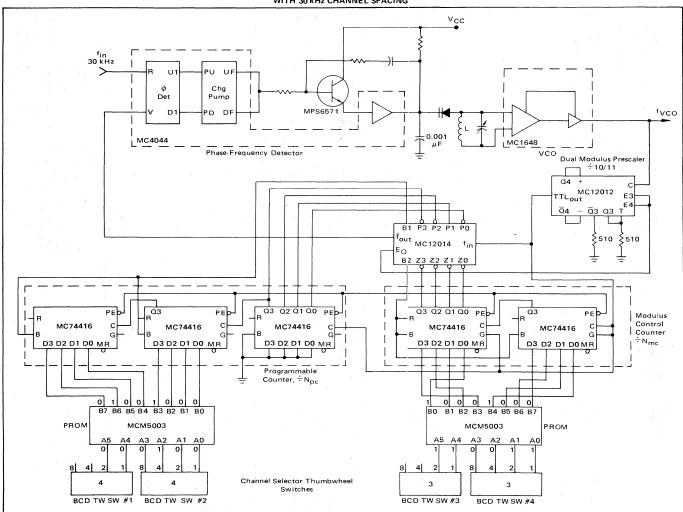

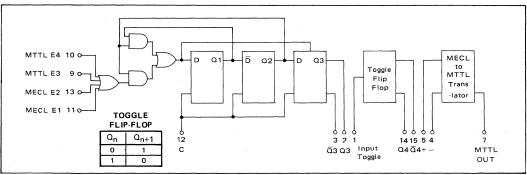

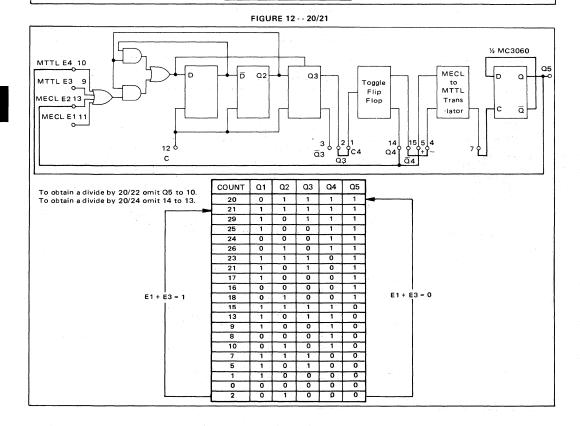

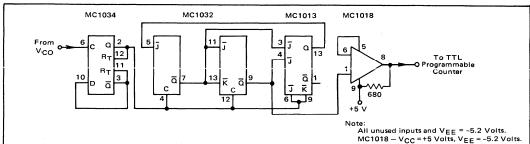

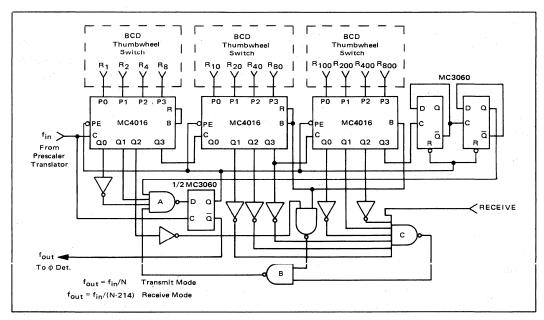

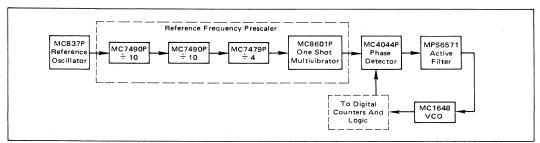

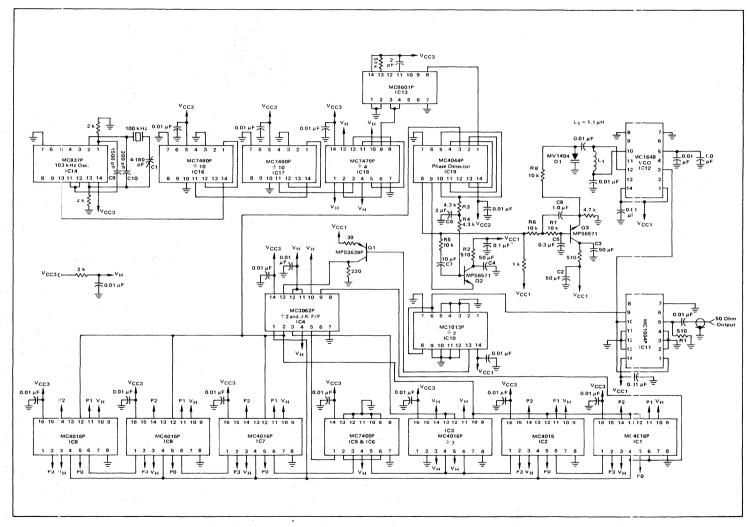

## The Technique Of Direct Programming By Utilizing A Two Modulus Prescaler (MC12012)

The disadvantage of using a fixed modulus (÷ P) for frequency division in high frequency phase-locked loops (cf Figure 16) is that it also requires

dividing the desired reference frequency by P (desired reference frequency equals channel spacing).

The MC12012 is specially designed for use with a technique called "variable modulus prescaling". This technique allows a simple MECL two-modulus prescaler (MC12012) to be controlled by a relatively slow MTTL programmable counter. The use of this technique permits direct high-frequency prescaling without any sacrifice in resolution since it is no longer necessary to divide the reference frequency by the modulus of the high frequency prescaler.

The theory of "variable modulus prescaling" may be explained by considering the system shown in Figure 16. For the loop shown:

$$f_{out} = NPf_{ref},$$

(1)

where P is fixed, and N is variable. For a change of 1 in N, the output frequency changes by Pf<sub>ref</sub>. If f<sub>ref</sub> equals the desired channel spacing, then only every P channel may be programmed using this method. A problem remains: how to program intermediate channels.

One solution to this problem is shown in Figure 3.  $A \div P$  is placed in series with the desired channel spacing to give a reference frequency: channel spacing/P.

Another solution is found by considering the defining equation (1) for f<sub>Out</sub> of Figure 16. From the equation it may be seen that only every P channel can be programmed simply, because N is always an integer. To obtain intermediate channels, P must be multiplied by an integer plus a fraction. This fraction would be of the form: A/P. If N is defined to be an integer number, Np, plus a fraction, A/P, N may be expressed as:

$$N = Np + A/P$$

Substituting this expression for N in equation 1 gives:

$$f_{Out} = (N_P + A/P) \cdot P \cdot f_{ref};$$

(2)

or:

$$f_{Out} = (NPP + A) \cdot f_{ref}$$

, (3)

$$f_{Out} = Np \cdot f_{ref} + A \cdot f_{ref}$$

(4)

Equation 4 shows that all channels can be obtained directly if N can take on fractional values. Since it is difficult to multiply by a fractional number, equation 4 must be synthesized by some other means.

Taking equation 3 and adding  $\pm AP$  to the coefficient of  $f_{ref}$ , the equation becomes:

$$f_{out} = (Np \cdot P + A + A \cdot P - A \cdot P) f_{ref}.$$

(5)

Collecting terms and factoring gives:

$$f_{out} = [(N_P - A) P + A (P + 1)] f_{ref.}$$

(6)

From equation 6 it becomes apparent that the fractional part of N can be synthesized by using a two-modulus counter (P and P+1) and dividing by the upper modulus, A times, and the lower modulus, (Np – A) times.

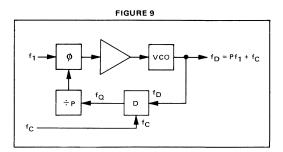

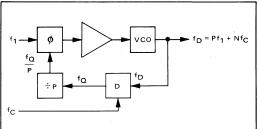

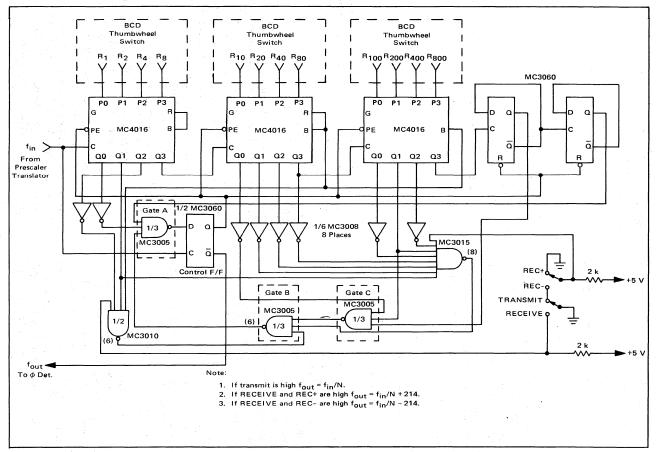

This equation (6) suggests the circuit configuration in Figure 17. The A counter shown must be the type that counts from the programmed state (A) to the

enable state, and remains in this state until divide by Np is completed in the programmable counter.

In operation, the prescaler divides by P+1, A times. For every P+1 pulse into the prescaler, both the A counter and the Np counter are decremented by 1. The prescaler divides by P+1 until the A counter reaches the zero state. At the end of (P+1)  $\cdot$  A pulses, the state of the Np counter equals (Np - A). The modulus of the prescaler then changes to P. The variable modulus counter divides by P until the remaining count, (Np - A) in the Np counter, is decremented to zero. Finally, when this is completed, the A and Np counters are reset and the cycle repeats.

To further understand this prescaling technique, consider the case with P = 10. Equation 6 becomes:

$$f_{out} = (A + 10Np) \cdot f_{ref}.$$

(7)

If Np consists of 2 decades of counters then:

$N_P = 10N_0 + N_1$  ( $N_0$  is the most significant digit), and equation 7 becomes:

$$f_{out} = (100 N_0 + 10 N_1 + A) f_{ref}$$

.

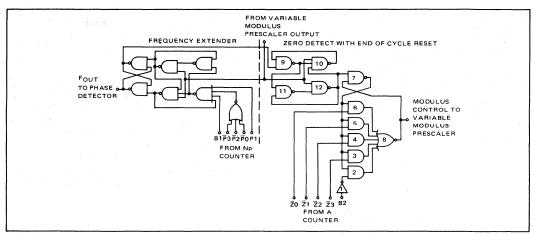

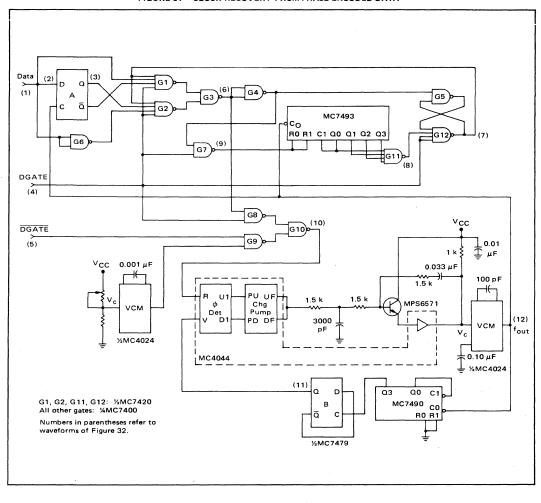

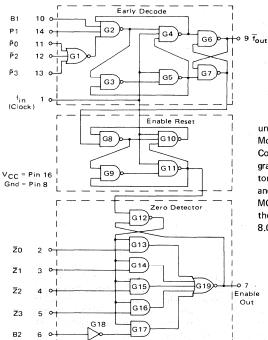

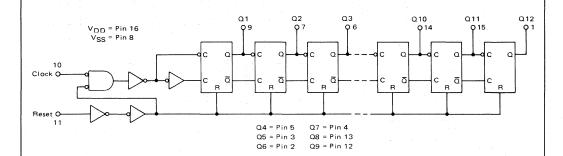

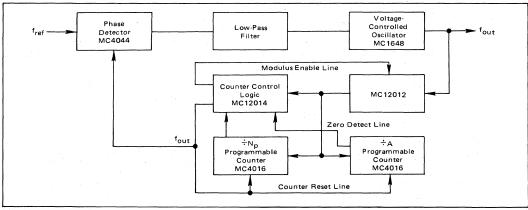

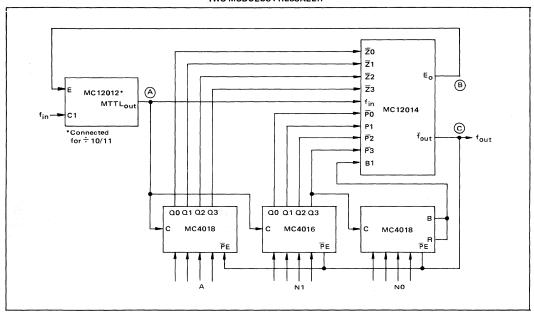

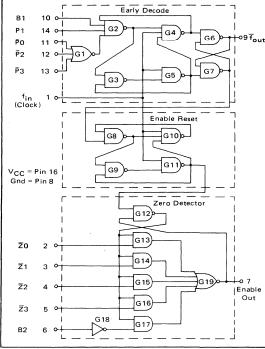

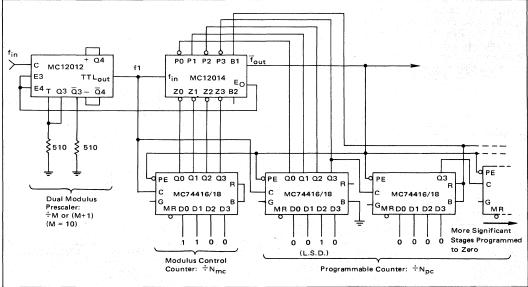

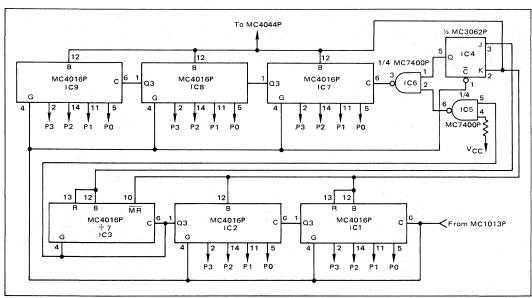

#### Counter Control Logic (MC12014)

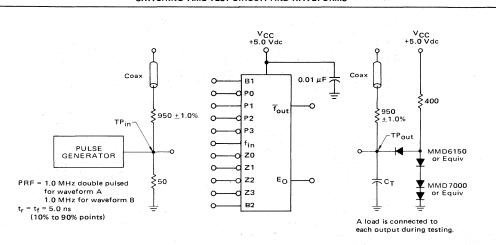

If the two-modulus prescaler is to operate at frequencies in excess of 200 MHz, then the counters following the prescaler must operate above 20 MHz (basic mode of operation of the prescaler being  $\div$  10). The programmable counters have a maximum frequency of approximately 8 MHz without the frequency extender.

A circuit to control the variable modulus counter and extend the frequency of operation of the divide by Np and A counters is shown in Figure 18. Gates 1 through 8 form a latch which goes to a 1 state and remains there when a 0 appears on  $\overline{Z}_0$ ,  $\overline{Z}_1$ ,  $\overline{Z}_2$  and  $\overline{Z}_3$ , and a 1 appears on B2. The B2 input is required only when more than 1 programmable counter is used for the  $\div$  A counter. Once set to a 1, the output of gate 8 remains at 1 regardless of the states appearing at inputs  $\overline{Z}_0$ ,  $\overline{Z}_1$ ,  $\overline{Z}_2$ ,  $\overline{Z}_3$  and B2, and can be reset to 0 only by an input from the circuit comprised of gates 9 through 12. Gates 9 through 12 are used to determine the end of a divide cycle.

The output of the frequency extender is sampled on every positive transition of the clock input. When the output of the extender goes high signifying the end of a cycle, gates 9 through 12 are enabled and the latch is reset on the next positive transition of the clock. The operation of these parts may be further clarified by considering the complete system shown in Figure 19.

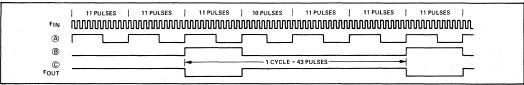

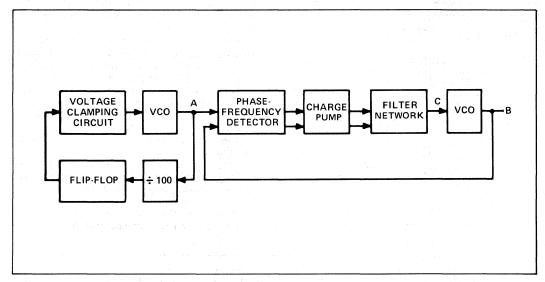

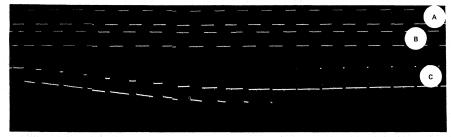

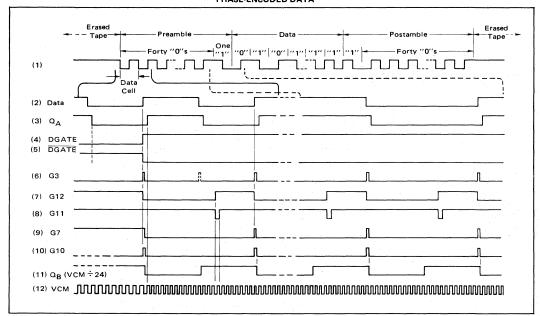

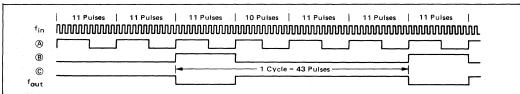

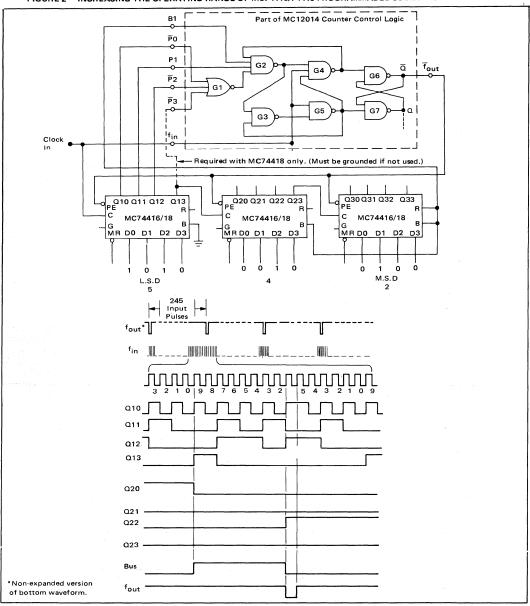

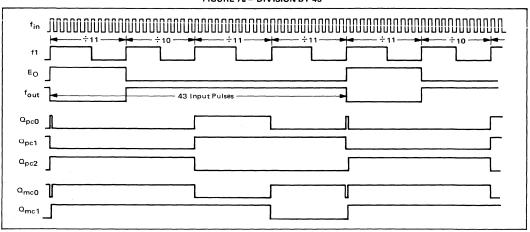

To understand the operation of the system shown in Figure 19, consider the case in which it is desired to divide by 43. This is accomplished by programming  $N_0 = \emptyset$ ,  $N_1 = 4$ , and A = 3. The waveforms for various points in the circuit are shown in Figure 20 for this division.

From the waveforms it may be seen that the two-modulus prescaler starts in the  $\div$  11 mode. The first pulse causes point A to go high. This positive transition decrements the upper counter to 3 and the

Figure 18 - Counter Control Logic

Figure 19 — Direct Programming Using a Two Modulus Prescaler

Figure 20 - Waveforms for Division by 43

Figure 21 — Waveforms for Division by 42

Figure 22 - Waveforms for Division by 44

lower counter to 2. After 11 pulses point A again goes high and decrements the upper counter to 2 and the lower counter to 1. The 2 contained in the upper counter enables the inputs to the frequency extender.

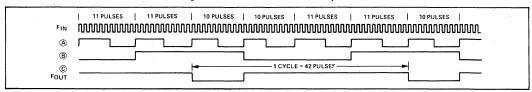

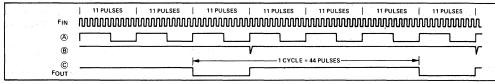

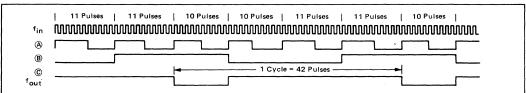

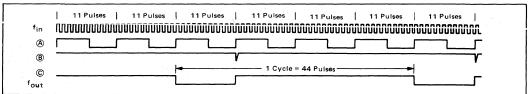

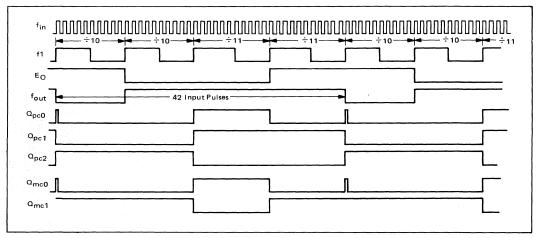

After 11 more pulses point A goes high again. With this positive transition, the output (fout) of the extender goes low, the upper counter goes to 1, and the lower counter goes to Ø. Point B goes to 1 and will change the modulus to 10 at the start of the cycle. When fout goes low, the programmable counters are reset to the programmed number. After 11 pulses (the enable went high after the start of the cycle and therefore doesn't change the modulus until the next cycle), point A makes another positive transition. This positive transition causes fout to return high, releases the preset on the counters, and generates a pulse to clear the latch (return point B to 0). After 10 pulses the cycle begins again (Point B was high prior to point A going high). The number of input pulses that have occurred for this operation is 3  $\times$  11 + 10 = 43. Figures 21 and 22 show the waveforms for  $\div$  42 and  $\div$  44 respectively.

This method may be used in any application as long as the number in the Np counter is larger or equal to the number in the A counter. Failure to observe this rule will result in erroneous results. For

example, for the system shown in Figure 20 if the number 45 is programmed the circuit will divide by 44.

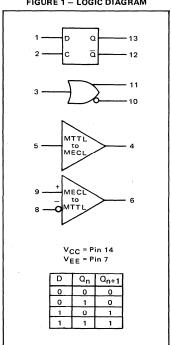

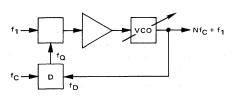

#### Digital Mixing (MC12000)

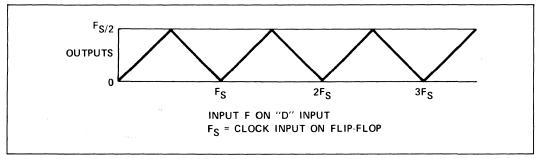

The operation of the "D" flip-flop as a mixer may be understood if it is regarded as a binary zero-order-hold filter. If the input is a logic 1 when the clock makes its transition the output goes to and remains a 1 for a full clock period. If it were at a 1 from the previous time, it remains at a 1. The same is true for logic 0 inputs.

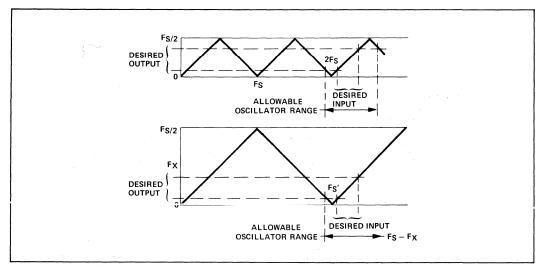

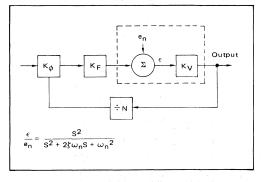

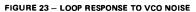

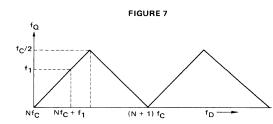

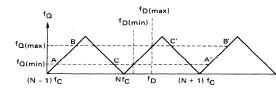

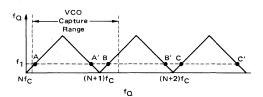

Of prime interest is the output frequency rather than the amplitude. The output "sequency" as a function of input frequency is shown in Figure 23. The word sequency is used to describe the output waveform, because the proper number of waveform edges occur per given length of time although they may not be evenly spaced. However, the filter in the loop can be adjusted to compensate for this. It is interesting to note the harmonic relation of the sampling frequency to the input and output functions. Figure 24 illustrates, for example, that the same output range can be achieved by using a mixing oscillator of one-half of the apparent mixing frequency. At this point it is of use to establish the

Figure 23 - Digital Mixer Transfer Function

Figure 24 — Harmonic Mixing

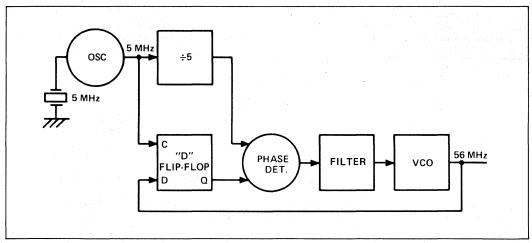

configuration of a system to see how this technique can be extended. Such a system is shown in Figure 25.

The conversion of the high frequency signal to a low frequency signal has forced the generation of a local oscillator frequency. This should be generated with as few components as possible. Applying the previously mentioned technique, the eleventh harmonic (55 MHz) of a reference (5 MHz) is mixed with 56 MHz from the VCO. This produces 1 MHz, which is used as the feedback to lock onto the reference frequency 1 MHz.

It is evident from this illustration that when mixing of this sort is used, the range of the VCO could lock at 51 or 61 MHz. It would not lock at 54 MHz or 59 MHz since the slope is in the wrong direction, but the information at the phase detector causes the system to "hang up" at either the high or low end of the VCO's range.

Figure 26 shows the range of interest for the system of Figure 25. It can be seen that if the input frequency is slightly less than 54 MHz the output

sequency is slightly greater than 1 MHz, so the loop responds by attempting to drive the VCO down in frequency. If the input frequency is slightly greater than 59 MHz, the output sequency is slightly less than 1 MHz, and the loop responds by trying to raise the VCO's frequency.

The VCO must therefore be restricted to operate above 54 MHz and below 59 MHz. This can be accomplished in a variety of ways: by the proper choice of a tuning diode with respect to the L and C values of the VCO tank; or by dc clamping of the input voltage to the VCO. Once the values are established with appropriate tolerances, this subsystem does not require alignment after assembly.

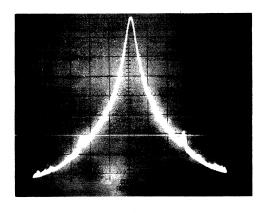

Of interest are the frequency spectra at various points in the circuit. Figure 27 shows the spectrum of the crystal oscillator. The shape of the curve in this case is determined by the analyzer. If the oscillator is delivering an absolutely pure sine wave the picture appears as shown.

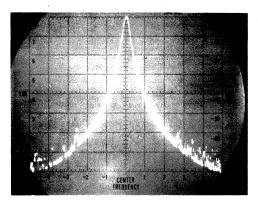

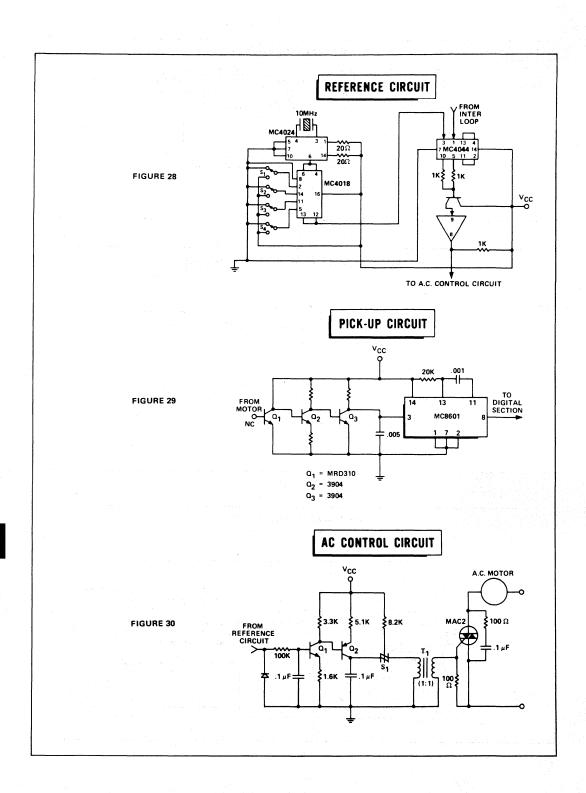

Figure 28 shows the spectrum of the 56 MHz oscillator. Again, the limiting factor in observing the

Figure 25 - Harmonic Mixing System

Figure 26 - Mixer Transfer Function

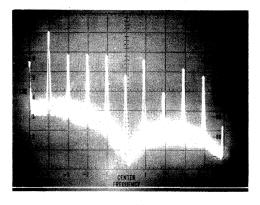

response is determined by the analyzer. It must be noted that while it is impossible to see exactly what the oscillator purity is, the output is down from the center frequency by at least 50 dB at plus or minus 300 Hz (considered the low end of the audio range useful for communication). The output from the mixer, Figure 29, is worth observing since the null at the 5 MHz sampling rate, as well as the 1 MHz peaks, can be seen.

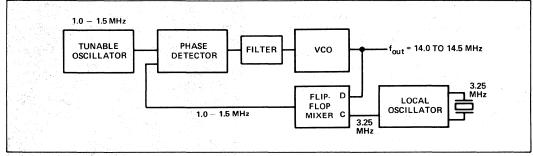

To illustrate the continuity of the mixing action, consider the system shown in Figure 30. A tunable oscillator of 1 MHz is used as the reference input to a loop whose tuning range has been restricted to greater than 12 MHz and less than 14.75 MHz. The local oscillator frequency is 3.25 MHz which gives an apparent mixing frequency (4  $\times$  3.25) of 12 MHz. Since the input oscillator is tunable, there is no guarantee of phase coherence between it and the crystal controlled reference oscillator.

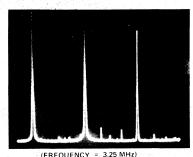

Figures 31, 32, and 33 show the respective local oscillator, mixer output, and reference oscillator spectra. Since they are all on the same scale, a comparison reveals that nulls on the mixer are produced at the harmonics of the mixer frequency, and that the first maximum of the mixer output is coincident with the fundamental of the reference oscillator.

As the reference frequency is tuned from 1 MHz to 1.5 MHz (although it is not possible to measure at the infinite number of frequencies between these two limits and guarantee a one to one correspondence), no evidence of sporadic operation is noted. While the reference is swept, a frequency ratio counter connected at the inputs of the phase detector always measures 1.000000.

The gain constant of the mixer can be found by examining the change in output frequency with respect to input frequency. Examination of Figure 26 shows this to be plus or minus one, depending on the slope that the input frequency intersects. An experimental method of proving this is to put a step change of frequency into the reference input of the loop shown in Figure 30. The VCO is restricted to operate on several different slopes of the mixing curve and the filter response examined. In all cases the waveforms are identical.

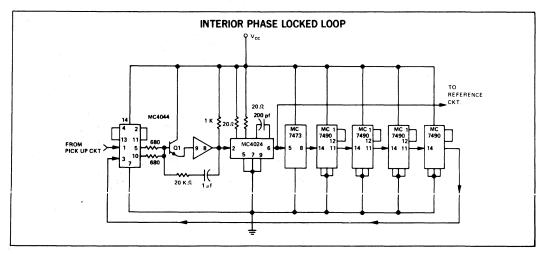

#### Phase Detection (MC4044)

The phase detection system is perhaps the most important part of the system. Noise and sidebands present in the loop are directly related to the output amplitude and waveform. Prior systems have used analog multipliers as phase detectors in which the output contains sum and difference frequencies. The sum frequencies are filtered out, and the loop tries to reduce the difference frequency to zero.

A digital form of multiplier is an Exclusive-OR gate. In this application a symmetrical square wave at twice the reference frequency represents the locked condition. Phase error is represented by asymmetry in the output waveform. In both these systems, lock

BANDWIDTH 50 Hz SCAN WIDTH 200 Hz/cm CENTER FREQUENCY 5 MHz

Figure 27 - Reference Oscillator Spectrum

BANDWIDTH 50 Hz SCAN WIDTH 200 Hz/cm CENTER FREQUENCY 56 MHz

Figure 28 - VCO Output Spectrum

BANDWIDTH 40 kHz SCAN WIDTH 1 MHz/cm CENTER FREQUENCY 5 MHz

Figure 29 - Mixer Output Spectrum

Figure 30 - Non-Coherent Mixing System

BANDWIDTH = 10 kHz

SCAN WIDTH = 1 MHz/cm

CENTER FREQUENCY = 4 MHz

Figure 31- Local Oscillator Spectrum

BANDWIDTH = 10 kHz SCAN WIDTH = 1 MHz CENTER FREQUENCY = 4 MHz

Figure 32 - Mixer Output Spectrum

(FUNDAMENTAL 1 MHz)

BANDWIDTH = 10 kHz

SCAN WIDTH = 1 MHz/cm

CENTER FREQUENCY = 4 MHz

Figure 33 - Reference Oscillator Spectrum

occurs when the phase error is  $90^\circ$ . The primary disadvantage of these systems is the feed-through at twice the reference frequency. This requires a high degree of attenuation in the loop filter (at  $2f_r$ ) to prevent frequency modulation of the voltage controlled oscillator.

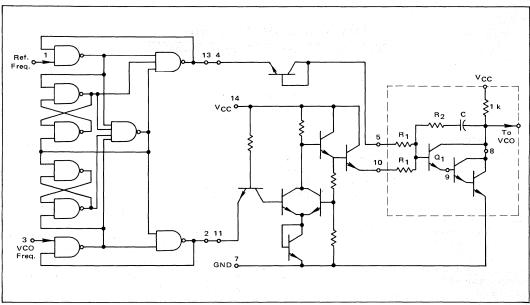

On close examination it appears that a lower noise method for phase locking in a digital system could be achieved if the "edges" of the reference and feedback frequencies could be matched in time with the error voltage proportional to the time differential (phase error). For the TTL family it is easier to provide the edge matching function of the falling edges (logic 1 to logic Ø transition) of the waveform.

It is also desirable to be insensitive to the duty cycle of the two inputs. This is necessary in the proposed systems since the duty of the programmable divider changes with N. In addition, the phase detection system must be able to discriminate frequency. This is important if a tuning range of greater than two to one is used. Prior systems generally were prone to locking on harmonics of the reference frequency.

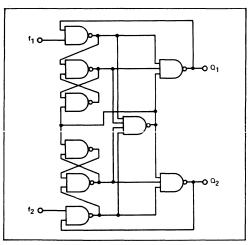

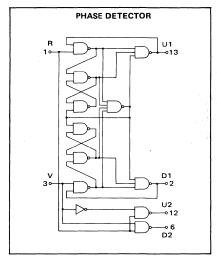

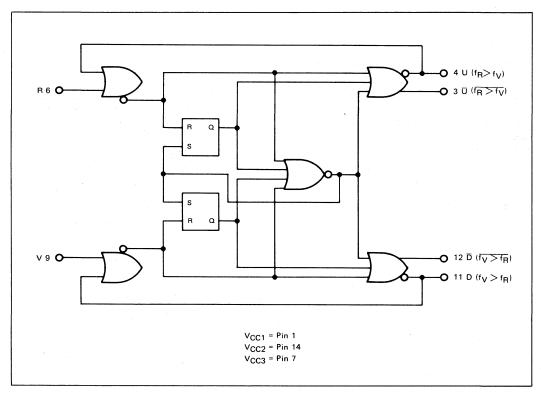

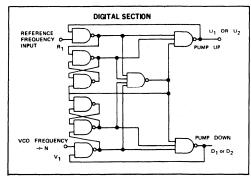

The logic required to perform this function is shown in Figure 34. This circuit contains storage for detecting a negative transition at each input, and logic for resetting the outputs if a negative transition occurs at both inputs.

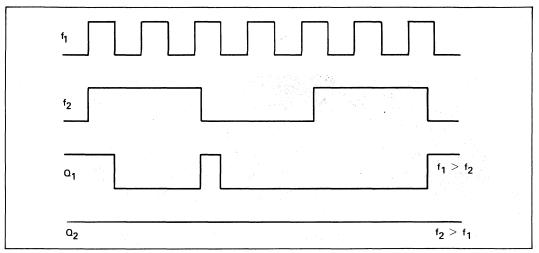

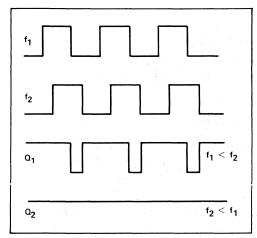

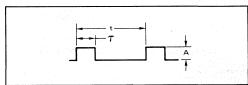

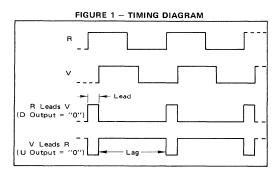

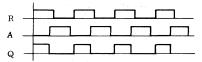

To understand the operation in the system observe the waveforms of Figure 35. Notice that both outputs are initially at the 1 state. The output representing  $f_1 > f_2$  is pulsed to the 0 state and reset at the rate of  $f_2$ . The minimum duty cycle of the 0 level is  $(1 - f_2/f_1) \cdot 100\%$ , and is cyclic at the rate of  $f_2$ .

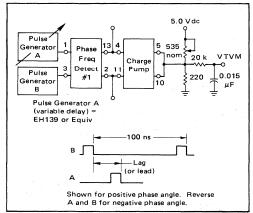

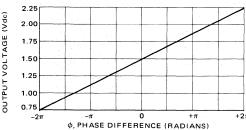

Figure 36 shows f<sub>1</sub> equal to f<sub>2</sub> but leading in phase. The output width is equal to the time difference between the edges of f<sub>1</sub> and f<sub>2</sub>. When the system is in lock, the pulse output of the phase detector is nonexistent; therefore, the filtering requirement is minimal.

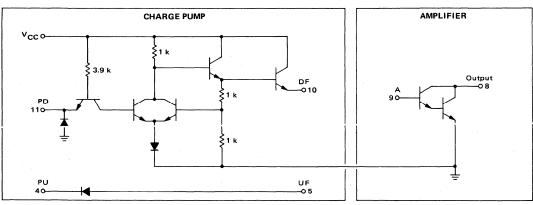

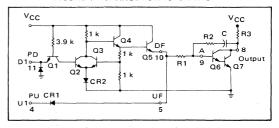

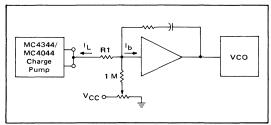

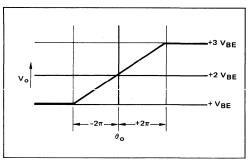

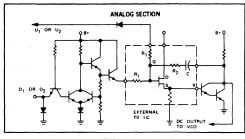

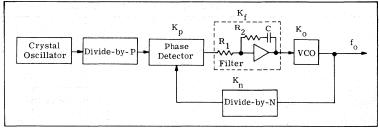

At this point in the system it is necessary to make the transformation from digital to analog. This is done with the use of a "charge pump" circuit which produces plus or minus one diode drop with respect to two diode drops to ground.

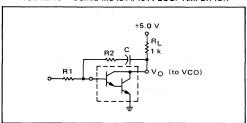

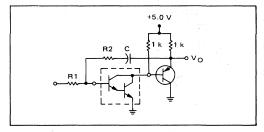

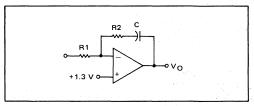

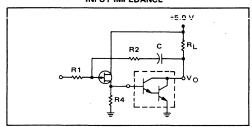

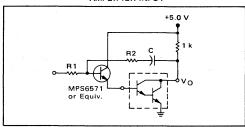

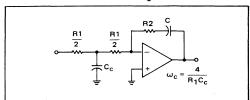

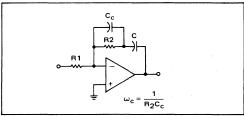

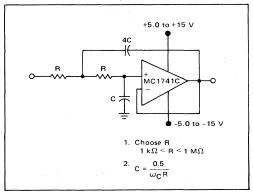

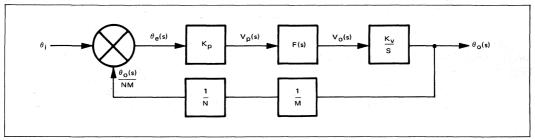

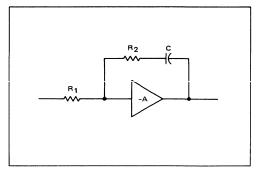

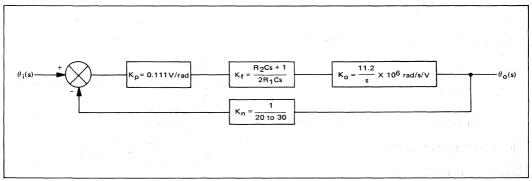

The gain of the phase detector is V/2  $\pi$  ( $\Phi_{\rm f}$  -  $\Phi_{\rm f}$ ). This voltage is applied to an amplifier with a two diode dc threshold as shown in Figure 37. The amplifier also serves as an active filter whose transfer

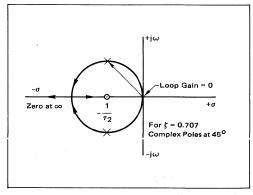

Figure 34 — Digital Phase Detector

function for  $R_1 \ge R_2$  is:  $(1 + R_2C_s)/R_1C_s$ .  $R_1$ ,  $R_2$ , and C determine the time constants for the loop response.

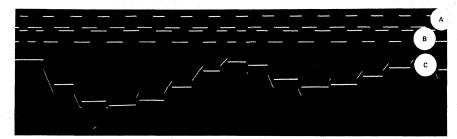

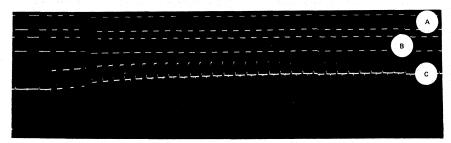

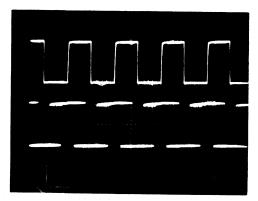

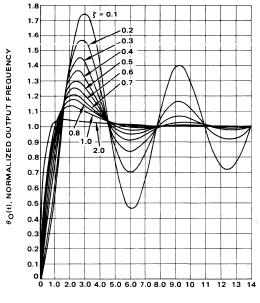

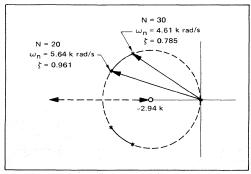

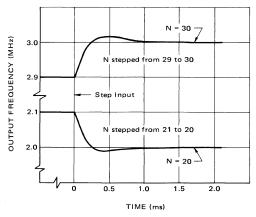

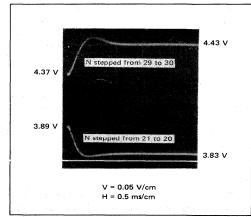

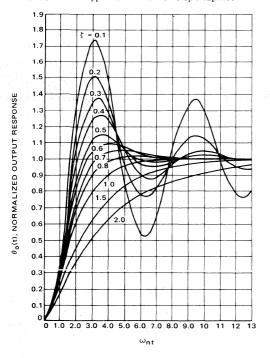

For a dynamic illustration of this operation consider the system of Figure 38. The first oscillator puts out 100 pulses at each of two different frequencies. This allows a step change in frequency to be applied to a loop so that the response to a step change can be examined. The underdamped, overdamped, and critically damped cases are shown in Figures 39, 40 and 41 respectively, with A representing the input, B the output, and C the voltage input to the oscillator.

The voltage applied to the oscillator is the superposition of the "pump up" and "pump down" pulses from the charge pump, on the dc level that controls the oscillator frequency.

When using the phase detector in the mixing system, it is important to note that the outputs are

Figure 35 — Timing Diagram: Phase Detector with Different Frequency Inputs

Figure 36 — Phase Detector with Equal Input Frequencies of Differing Phases

Figure 37 - Active Filter

Figure 38 — System for Measuring Loop Response

Figure 39 - Underdamped System

Figure 40 — Overdamped System

Figure 41 — Critically Damped System

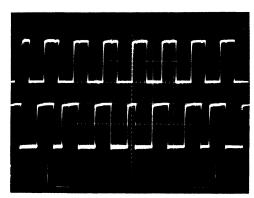

TOP TRACE IS REFERENCE OSCILLATOR BOTTOM TRACE IS MIXER OUTPUT VERTICAL = 2V/DIV. HORIZONTAL =  $0.5 \mu s/DIV$ .

Figure 42 - Reference Oscillator and Mixer Output

TOP TRACE IS REFERENCE OSCILLATOR BOTTOM TRACE IS MIXER OUTPUT VERTICAL = 2V/DIV. HORIZONTAL UNCALIBRATED

Figure 43 — Reference Oscillator and Mixer Output

always changing. It may be said that the system is never in lock, taking literally the previous definition that the error goes to zero. What the system is achieving is a stable condition based on the same number of negative transitions occurring for the feedback and for the reference (per unit time).

For the system shown in Figure 30, Figures 42 and 43 show the two inputs to the phase detector. The reference is purposely made continuously tunable so that a lack of coherency is achieved between the mixing frequency and the reference. In Figure 42, the oscilloscope is synchronized with the reference oscillator, and the mixer output transitions are time averaged and appear as a smear. In Figure 43 the oscilloscope is synchronized on the mixer output so that the irregularity of the waveform can be observed.

#### **TERMINOLOGY**

| PLL            | Phase-Locked Loop                         |

|----------------|-------------------------------------------|

| ÷              | "divide by"                               |

| N              | An integer                                |

| VCO            | Voltage Controlled Oscillator             |

| F (s)          | A filter                                  |

| $\phi$         | Phase detector                            |

| $f_0$          | output frequency                          |

| VCM            | Voltage Controlled Multivibrator          |

| TTL            | Transistor Transistor Logic               |

| ECL            | Emitter Coupled Logic                     |

| fm             | Mixing frequency, from a local oscillator |

| NBCD           | Natural Binary Coded Decimal (code)       |

| MSD            | Most significant Digit                    |

| LSD            | Least significant Digit                   |

| f <sub>r</sub> | Reference Frequency                       |

## **PHASE-DETECTORS**

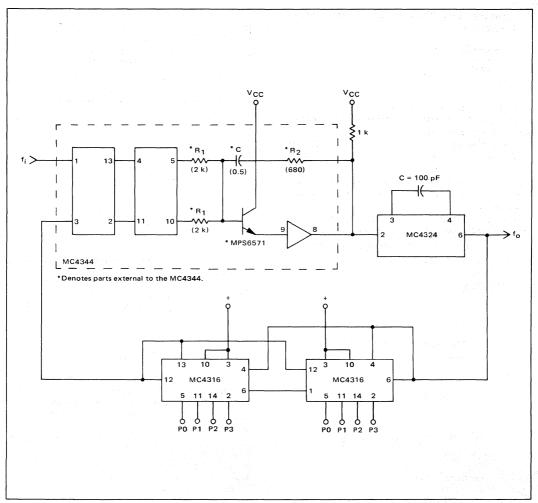

#### PHASE-FREQUENCY DETECTOR

#### MC4344 • MC4044

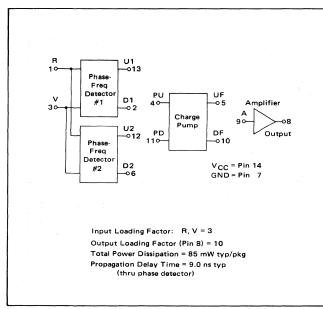

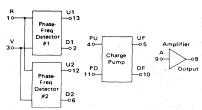

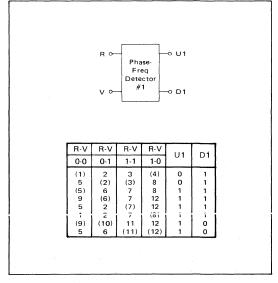

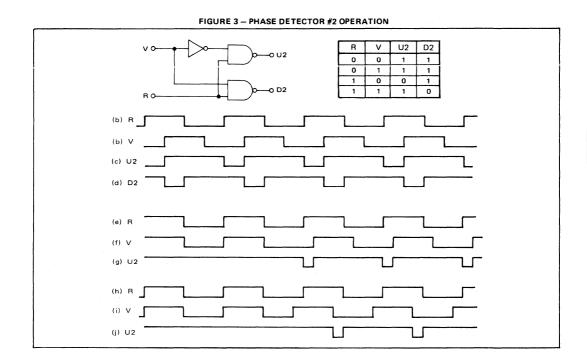

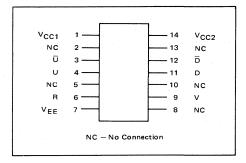

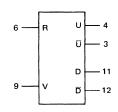

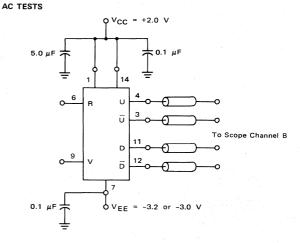

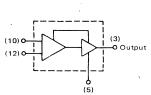

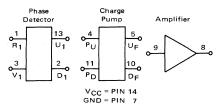

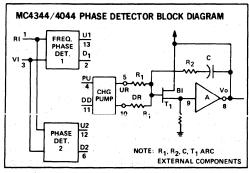

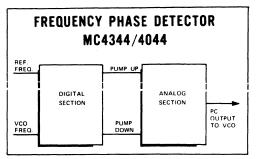

The MC4344/4044 consists of two digital phase detectors, a charge pump, and an amplifier. In combination with a voltage controlled multivibrator (such as the MC4324/4024 or MC1648), it is useful in a broad range of phase-locked loop applications. The circuit accepts MTTL waveforms at the R and V inputs and generates an error voltage that is proportional to the frequency and/or phase difference of the input signals. Phase detector #1 is intended for use in systems requiring zero frequency and phase difference at lock. Phase detector #2 is used if quadrature lock is desired. Phase detector #2 can also be used to indicate that the main loop, utilizing phase detector #1, is out of lock.

#### **ELECTRICAL CHARACTERISTICS**

| INPUT | INF                   | PUT |     | OUTPUT |     |    |  |  |  |  |  |

|-------|-----------------------|-----|-----|--------|-----|----|--|--|--|--|--|

| STATE | RI                    | VI  | U1  | D1     | U2  | D2 |  |  |  |  |  |

| 1     | 0                     | 0.  | ×   | ×      | 1   | 1  |  |  |  |  |  |

| 2     | 1                     | 0   | ×   | ×××    | 0   | 1  |  |  |  |  |  |

| 3     | . 1                   | 1   | ×   | X      | 1 . | 0  |  |  |  |  |  |

| 4     | 1                     | 0   | ×   | X.     | 0   | 1  |  |  |  |  |  |

| 5     | 0                     | . 0 | ×   | ×      | 1   | 1  |  |  |  |  |  |

| 6     | 1                     | 0   | ×   | ×      | 0   | 1  |  |  |  |  |  |

| 7     | 0                     | 0   | ××× | X      | 1   | 1  |  |  |  |  |  |

| 8     | 1                     | 0   | X   | X      | 0   | 1  |  |  |  |  |  |

| 9     | 0                     | 0   | 0   | 1      | 1   | 1  |  |  |  |  |  |

| 10    | 0<br>0<br>0           | 1   | 0   | 1      | 1.  | 1. |  |  |  |  |  |

| 11    | 0                     | 0   | - 1 | 1      | 1   | 1  |  |  |  |  |  |

| 12    | 0                     | 1   | 11  | 1.     | . 1 | 1  |  |  |  |  |  |

| 13    | 0<br>0<br>0<br>1<br>0 | 0   | 1   | 0.     | 1   | 1  |  |  |  |  |  |

| 14    | 0                     | 1   | 1   | 0      | 1   | 1  |  |  |  |  |  |

| 15    | 0                     | 0   | 1   |        | 1   | 1  |  |  |  |  |  |

| 16    | 1                     | 0   | 1   | 0      | 0   | 1  |  |  |  |  |  |

| 17    | 0                     | 0   | 1   | 1      | 1   | 1  |  |  |  |  |  |

#### TRUTH TABLE

This is not strictly a functional truth table; i.e., it does not show all possible modes of operation. It is useful for dc testing.

- X indicates output state unknown.

- U1 and D1 outputs are sequential; i.e., they must be sequenced in order shown.

- U2 and D2 outputs are combinational; i.e., they need only inputs shown to obtain outputs.

TEST CURRENT/VOLTAGE VALUES

| Part      | Preq<br>Detector     |        |      | -        |          | - 1      |      |       |      |     |          |       |      |          |          | T        | L   |          | : mA             |                 |     |       | L_          |      |                                              |       | Vo    | lts  |              |      |              | 1        | 1  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------|------|----------|----------|----------|------|-------|------|-----|----------|-------|------|----------|----------|----------|-----|----------|------------------|-----------------|-----|-------|-------------|------|----------------------------------------------|-------|-------|------|--------------|------|--------------|----------|----|

| Part                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |        |      |          |          |          |      |       |      |     |          |       |      |          |          | perature |     |          |                  | 1 <sub>in</sub> |     |       |             |      | VIHH                                         |       |       |      |              |      |              |          | 1  |

| Part      |                      | -06    |      |          |          |          |      |       |      |     |          |       |      |          | . 1      |          |     |          |                  | -               |     |       |             |      |                                              |       |       |      |              |      |              |          |    |

| Second Current   Seco   |                      |        |      |          |          |          |      |       |      |     |          |       |      | MC434    |          |          |     |          |                  | 1.0             | -10 |       |             |      |                                              |       |       |      |              |      |              | 1        | 1  |

| Part                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |        |      |          |          |          |      |       |      |     |          |       |      |          | ì        |          |     |          |                  | -               | -   |       |             |      |                                              |       |       |      |              |      |              |          | 1  |

| Convenience   Paper    |                      |        |      |          |          |          |      |       |      |     |          |       |      | MC404    | 4 {      | +25°C    | 20  | -1.6     | -1.0             | 1.0             | -10 | 0.002 | 0.4         |      | 5.5                                          | 1.1   | 1.8   | 1.5  | 5.0          |      |              | 1        |    |

| The property of the property o |                      |        |      |          |          |          |      |       | 4.1  |     |          |       |      |          |          | +75°C    | 20  | -1.6     | -1.0             | -               | -   | 0.002 | 0.4         | 2.5  | -                                            | 0.9   | 1.8   | 1.5  | 5.0          | 4.75 | 5.25         |          |    |

| Control Current   Control Cu   |                      |        |      | <u> </u> |          | _        |      | _     | -00  | _   |          |       |      |          | -0-      | _        |     |          | TES              | CUR             | REN | T/VO  | LTAG        | E AP | PLIED                                        | TO PI | NS LI | STED | BELOV        | V:   |              |          | ì  |

| From the Current   11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Characteristic       | Symbol |      |          |          |          |      |       |      |     |          |       |      |          |          | Unit     | loL | ЮН1      | I <sub>OH2</sub> | lin             | lic | IA .  | VIL         | VIH  | VIHH                                         | VILT  | VIHT  | Vout | Vcc          | VCCL | VCCH         |          |    |

| Semble Current   Fig. 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      | 11L    |      | =        | -4.8     | =        | -4.8 |       | -4.8 | Ξ   | -4.8     | =     | -4.8 | =        | -4.8     | mAdc     | -   | =        | =                | = 1             | -   | -     | 3           | -    | -                                            | 1 1   | 1 1   | 1_   | =            | =    | 14           | =        |    |

| Series   S   | eakage Current       | liu    |      | -        |          | +        |      | -     |      | =   |          | 1     |      | <u> </u> |          | u Adc    | =   | -        | <del>-</del>     | -               | -   | -     | 11          | -    |                                              |       |       |      | -            |      | 1.           | -        | ╀  |

| The control of the    |                      | , '''  | 3    |          | 120      | -        | 120  | -     | 120  | -   | 120      | -     | 120  | -        | 120      |          | -   | -        | -                |                 | Ξ   | -     |             | 3    |                                              | -     | -     | -    | -            | -    | 14           | =        |    |

| Improviding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |        |      |          | 40       | -        | 40   | -     | 40   | =   |          |       |      | _        |          | 1        | _   | 1 =      |                  |                 | _   |       | 1= 1        | 11   | _                                            |       |       | -    | ]            |      |              | -        |    |

| 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      | інн.   |      |          | -        | 1.0      |      |       |      |     |          | 1.0   | -    |          |          | mAdc     | -   |          | -                | -               | -   | -     | -           | -    |                                              |       | -     | -    | -            | -    | 14           | 7-       | T  |

| Serry Notings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      | 1      |      |          | -        | 1        |      |       |      |     |          |       | -    |          |          |          | =   | 1 -      |                  | -               |     | -     | -           | -    |                                              |       | -     | = 1  | -            |      | 1            | -        |    |

| Septiment (Notes)  VOH  S  VOH  S  VOH  S  VOH  S  VOH  S  S  S  S  S  S  S  S  S  S  S  S  S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | lamp Voltage         | Vic    |      | -        |          | +        | -    |       | -    | -   |          | -     | _    |          |          | Vdc      | -   | -        |                  | -               | _   |       | -           | -    |                                              | _     | _     | _    | <del>-</del> | 14   | Ė            | 1        | t  |

| Very Vorlage  Vol. 12 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      | 1.0    | 3    | -        | <u> </u> | <u> </u> |      |       |      | -   | -        |       |      | -        |          |          | -   | <u> </u> | -                | -               |     | -     | -           | -    |                                              | -     | -     |      | -            |      | -            | <u> </u> | L  |